UCC28063A

SNVSA88C - DECEMBER 2014-REVISED NOVEMBER 2016

# UCC28063A Natural Interleaving™ Transition-Mode PFC Controller With Improved Audible and Input Surge Noise Immunity

#### **Features**

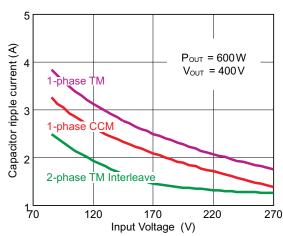

- Input Filter and Output Capacitor Ripple-Current Cancellation

- Reduced Current Ripple for Higher System Reliability and Smaller Bulk Capacitor

- Reduced EMI Filter Size

- Phase Management Capability

- Fail-Safe OVP with Dual Paths Prevents Output Overvoltage Conditions by Voltage-Sensing **Failures**

- Sensorless Current-Shaping Simplifies Board Layout and Improves Efficiency

- Advanced Audible Noise Performance

- Non-linear Error-Amplifier Gain

- Soft Recovery on Overvoltage

- Integrated Brownout and Dropout Handling

- Reduced Bias Currents

- Improved Efficiency and Design Flexibility Over Traditional Single-Phase Continuous Conduction Mode (CCM)

- Inrush-Safe Current Limiting:

- Prevents MOSFET Conduction During Inrush

- Eliminates reverse Recovery Events in Output rectifiers

- **Enables Use of Low-Cost Diodes Without Extensive Snubber Circuitry**

- Improved Light-Load Efficiency

- Fast, Smooth Transient Response

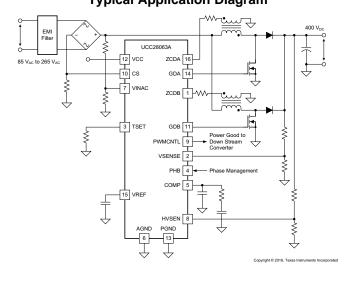

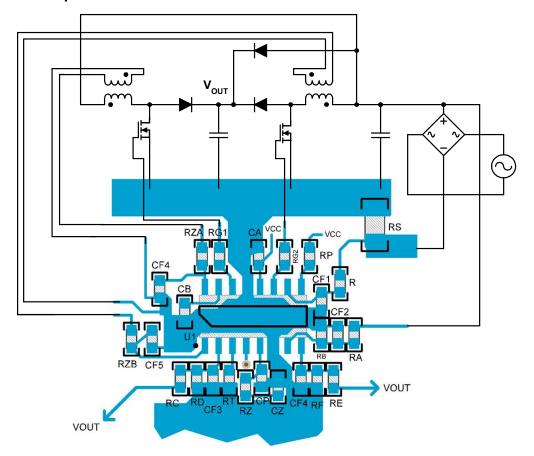

# **Typical Application Diagram**

- **Expanded System-Level Protections**

- 1-A Source/1.8-A Sink Gate Drivers

- -40°C to 125°C Operating Temperature Range in a 16-Lead SOIC Package

# **Applications**

- 100-W to 800-W Power Supplies

- Gaming

- D-to-A Set-Top Boxes

- Adapters

- LCD, Plasma and DLP™ TVs

- Home Audio Systems

# Description

This part is identical to UCC28063 with the exception that the TSET pin Open/ Short Fault Detect and the CS pin Open Fault Detect features are removed. Removal of these Fault Detect features provides a higher degree of noise immunity to provide increased "ride-through" for applications where significant voltage noise could be coupled onto the TSET or CS pins during conditions of fast transient, surge or impulse noise on the AC Supply.

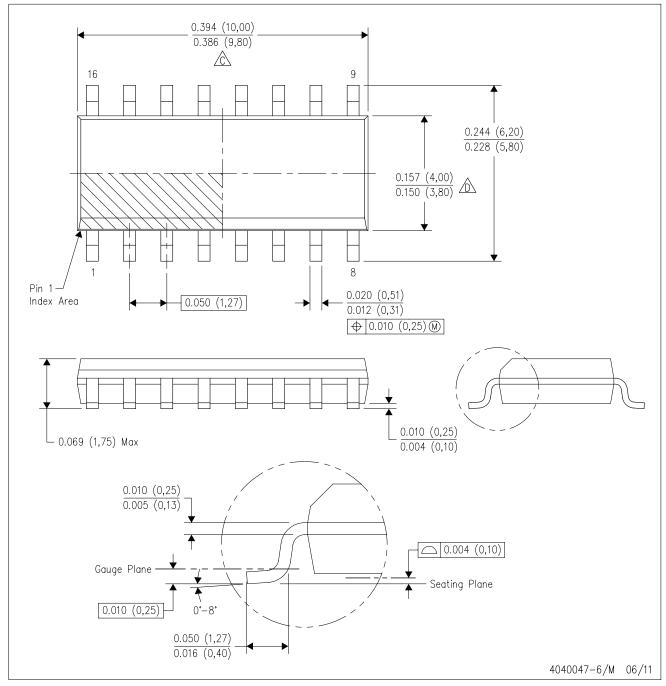

# Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| UCC28063A   | SOIC (16) | 9.90 mm × 3.91 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

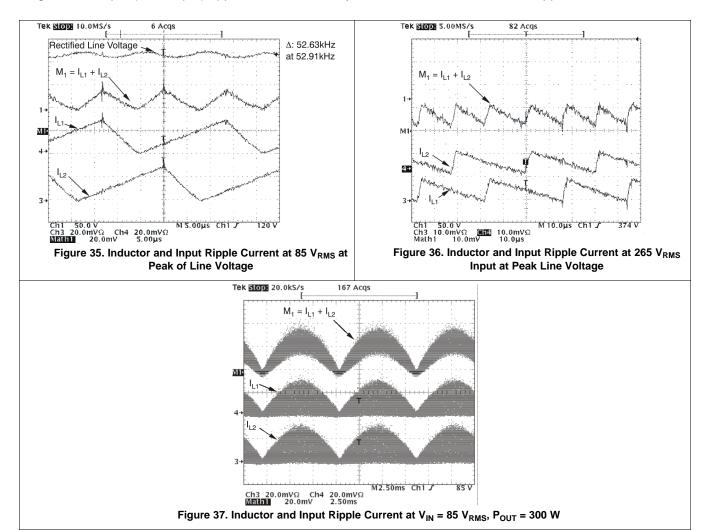

# Input Ripple Current Reduction with Interleaving

Ripple Current Reduction

# **Table of Contents**

| 1 | Features 1                           |    | 8.3 Feature Description                          | 15              |

|---|--------------------------------------|----|--------------------------------------------------|-----------------|

| 2 | Applications 1                       |    | 8.4 Device Functional Modes                      | <mark>27</mark> |

| 3 | Description 1                        | 9  | Applications and Implementation                  | 28              |

| 4 | Revision History2                    |    | 9.1 Application Information                      | 28              |

| 5 | Description (Continued)3             |    | 9.2 Typical Application                          | 28              |

| 6 | Pin Configuration and Functions      | 10 | Power Supply Recommendations                     | 35              |

| 7 | Specifications4                      | 11 | Layout                                           | 36              |

| • | 7.1 Absolute Maximum Ratings         |    | 11.1 Layout Guidelines                           | 36              |

|   | 7.2 ESD Ratings                      |    | 11.2 Layout Example                              | 36              |

|   | 7.3 Recommended Operating Conditions | 12 | Device and Documentation Support                 | 37              |

|   | 7.4 Thermal Information              |    | 12.1 Device Support                              | 37              |

|   | 7.5 Electrical Characteristics       |    | 12.2 Documentation Support                       | 39              |

|   | 7.6 Typical Characteristics          |    | 12.3 Trademarks                                  | 39              |

| 8 | Detailed Description                 |    | 12.4 Electrostatic Discharge Caution             | 39              |

| • | 8.1 Overview                         |    | 12.5 Glossary                                    | 39              |

|   | 8.2 Functional Block Diagram         | 13 | Mechanical, Packaging, and Orderable Information | 39              |

# 4 Revision History

| Changes from Revision B (March 2015) to Revision C    |      |

|-------------------------------------------------------|------|

| Added GDA, GDB Absolute Maximum ratings.              |      |

| Ohanna fran Badalan A (Fahman 2045) (a Badalan B      | D    |

| Changes from Revision A (February 2015) to Revision B | Page |

| Changed from Product Preview to Production Data       |      |

# 5 Description (Continued)

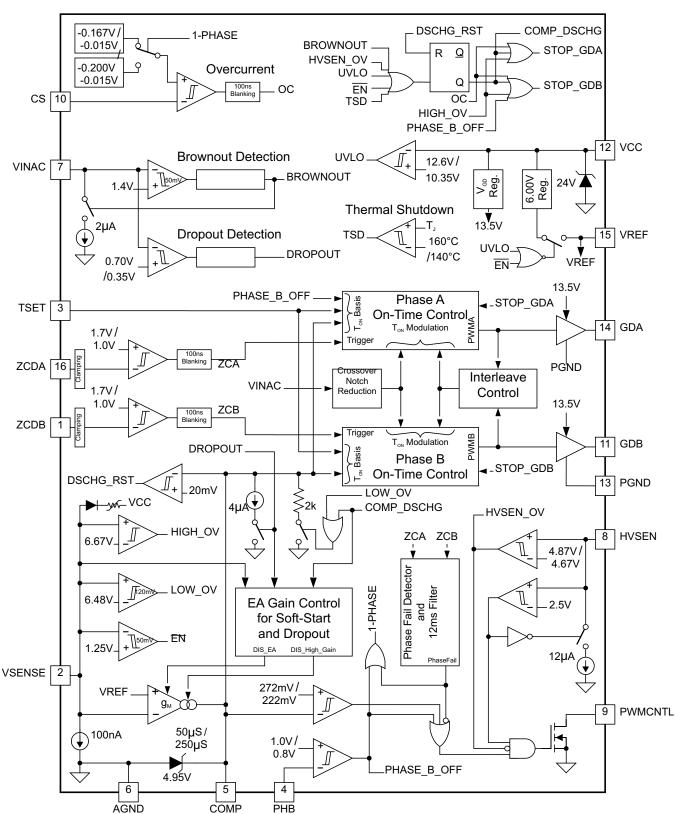

Optimized for consumer applications concerned with audible noise elimination, this solution extends the advantages of transition mode – high efficiency with low-cost components – to higher power ratings than previously possible. By utilizing a Natural Interleaving<sup>TM</sup> technique, both channels operate as masters (that is, there is no slave channel) synchronized to the same frequency. This approach delivers inherently strong matching, faster responses, and ensures that each channel operates in transition mode.

Expanded system level protections feature input brownout and dropout recovery, output over-voltage, open-loop, overload, soft-start, phase-fail detection, and thermal shutdown. The additional FailSafe over-voltage protection (OVP) feature protects against shorts to an intermediate voltage that, if undetected, could lead to catastrophic device failure. Advanced non-linear gain results in rapid, yet smoother response to line and load transient events. Reduced bias currents improve stand-by power efficiency. Special line-dropout handling avoids significant current disruption and minimizes audible-noise generation.

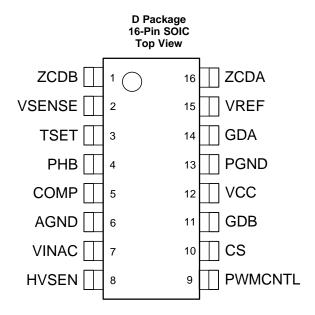

# 6 Pin Configuration and Functions

**Pin Functions**

| PI      | IN  | 1/0 | DESCRIPTION                               |  |

|---------|-----|-----|-------------------------------------------|--|

| NAME    | NO. | 1/0 | DESCRIPTION                               |  |

| AGND    | 6   | -   | Analog Ground                             |  |

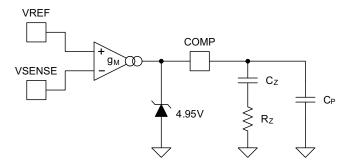

| COMP    | 5   | 0   | Error Amplifier Output                    |  |

| CS      | 10  | I   | Current Sense Input                       |  |

| GDA     | 14  | 0   | Channel A and Channel B Cata Drive Output |  |

| GDB     | 11  | 0   | Channel A and Channel B Gate Drive Output |  |

| HVSEN   | 8   | I   | High Voltage Output Sense                 |  |

| PHB     | 4   | I   | Phase-B Enable/Disable                    |  |

| PWMCNTL | 9   | 0   | PWM-Control Output                        |  |

| TSET    | 3   | I   | Timing Set                                |  |

| VCC     | 12  | -   | Bias Supply Input                         |  |

| VINAC   | 7   | I   | Input AC Voltage Sense                    |  |

| VREF    | 15  | 0   | Voltage Reference Output                  |  |

| VSENSE  | 2   | I   | Output DC Voltage Sense                   |  |

| ZCDA    | 16  | I   | Zero Current Detection Inputs             |  |

| ZCDB    | 1   | I   | Zero Current Detection Inputs             |  |

Copyright © 2014–2016, Texas Instruments Incorporated

# 7 Specifications

# 7.1 Absolute Maximum Ratings<sup>(1)</sup>

All voltages are with respect to GND,  $\neg 40$  °C <  $T_J = T_A < 125$  °C, currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                  |                                     |                                                                                                | MIN  | MAX     | UNIT |

|------------------|-------------------------------------|------------------------------------------------------------------------------------------------|------|---------|------|

|                  |                                     | VCC <sup>(2)</sup>                                                                             | -0.5 | 21      |      |

|                  |                                     | PWMCNTL                                                                                        | -0.5 | 20      | Ī    |

|                  | Continuous input voltage            | COMP <sup>(3)</sup> , PHB, HVSEN <sup>(4)</sup> , VINAC <sup>(4)</sup> , VSENSE <sup>(4)</sup> | -0.5 | 7       | .,   |

|                  | range                               | ZCDA, ZCDB                                                                                     | -0.5 | 4       | V    |

|                  |                                     | CS <sup>(5)</sup>                                                                              | -0.5 | 3       | Ī    |

|                  |                                     | GDA, GDB <sup>(6)</sup>                                                                        | -0.5 | VCC+0.3 | ı    |

|                  |                                     | VCC                                                                                            |      | 20      |      |

|                  | Continuous input current            | PWMCNTL                                                                                        |      | 10      | Ī    |

|                  |                                     | ZCDA, ZCDB                                                                                     |      | ±5      |      |

|                  | Peak input current                  | cs                                                                                             |      | -30     | mA   |

|                  | Output current                      | VREF                                                                                           |      | -10     | Ī    |

|                  | Continuous gate current             | GDA, GDB <sup>(6)</sup>                                                                        |      | ±25     | Ī    |

| _                | harden Tananantan                   | Operating                                                                                      | -40  | 125     |      |

| $T_J$            | T <sub>J</sub> Junction Temperature | Storage                                                                                        | -65  | 150     | 00   |

| T <sub>SOL</sub> | Lead Temperature                    | Soldering, 10s                                                                                 |      | 260     | °C   |

| T <sub>stg</sub> | Storage temperature                 |                                                                                                | -40  | 125     |      |

- (1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those included under *Recommended Operating Conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods of time may affect device reliability.

- (2) Voltage on VCC is internally clamped. VCC may exceed the continuous absolute maximum input voltage rating if the source is current limited below the absolute maximum continuous VCC input current level.

- (3) In normal use, COMP is connected to capacitors and resistors and is internally limited in voltage swing.

- (4) In normal use, VINAC, VSENSE, and HVSEN are connected to high-value resistors and are internally limited in negative-voltage swing. Although not recommended for extended use, VINAC, VSENSE, and HVSEN can survive input currents as high as -10mA from negative voltage sources, and input currents as high as +0.5mA from positive voltage sources.

- (5) In normal use, CS is connected to a series resistor to limit peak input current during brief system line-inrush conditions. In these situations, negative voltage on CS may exceed the continuous absolute maximum rating.

- (6) No GDA or GDB current limiting is required when driving a power MOSFET gate. However, a small series resistor may be required to damp resonant ringing due to stray inductance.

#### 7.2 ESD Ratings

|             |                         |                                                                     | VALUE | UNIT |

|-------------|-------------------------|---------------------------------------------------------------------|-------|------|

|             |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±2000 |      |

| $V_{(ESD)}$ | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

All voltages are with respect to GND, -40 °C <  $T_J = T_A < 125$  °C, currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                                                | MIN  | MAX | UNIT  |

|------------------------------------------------|------|-----|-------|

| VCC input voltage from a low-impedance source  | 14   | 21  | V     |

| VCC input current from a high-impedance source | 8    | 18  | A     |

| VREF load current                              | 0    | -2  | -2 mA |

| VINAC input voltage                            | 0    | 6   | V     |

| ZCDA, ZCDB series resistor                     | 20   | 80  | kO    |

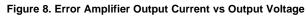

| TSET resistor to program PWM on-time           | 66.5 | 400 | kΩ    |

| HVSEN input voltage                            | 0.8  | 4.5 | V     |

# 7.4 Thermal Information

|                      |                                                             | UCC28063A |      |

|----------------------|-------------------------------------------------------------|-----------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                               | SOIC (D)  | UNIT |

|                      |                                                             | 16 PINS   |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance (2)                  | 91.6      |      |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance (3)               | 52.1      |      |

| $R_{\theta JB}$      | Junction-to-board thermal resistance (4)                    | 48.6      | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter <sup>(5)</sup>   | 14.9      |      |

| ΨЈВ                  | Junction-to-board characterization parameter <sup>(6)</sup> | 48.3      |      |

- For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report (SPRA953).

- (2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- (3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- (4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- (5) The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $R_{\theta JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

- (6) The junction-to-board characterization parameter, ψ<sub>JB</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining R<sub>θJA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

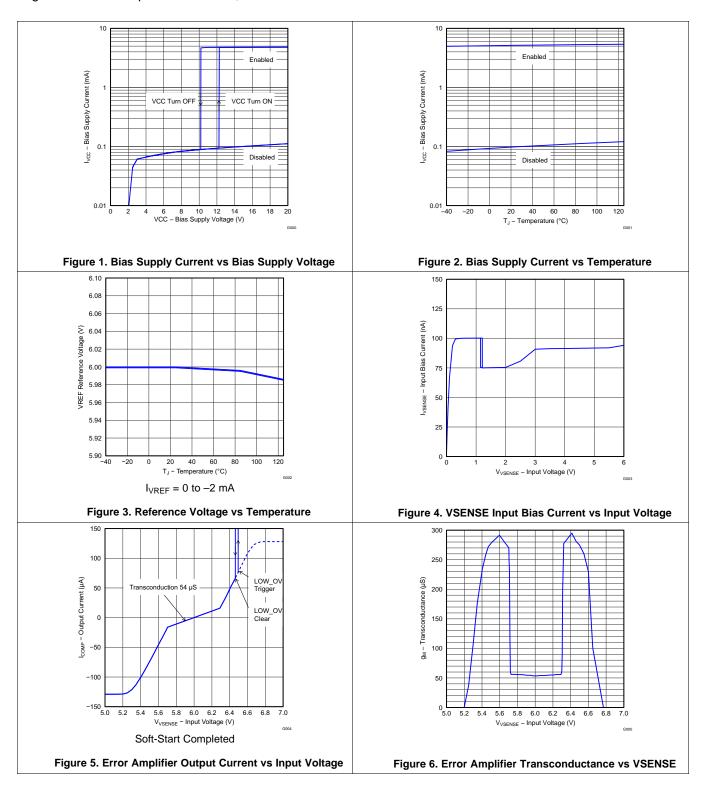

# 7.5 Electrical Characteristics

At VCC = 16 V, AGND = PGND = 0 V, VINAC = 3 V, VSENSE = 6 V, HVSEN = 3 V, PHB = 5 V,  $R_{TSET}$  = 133 k $\Omega$ , all voltages are with respect to GND, all outputs unloaded, -40 °C <  $T_J$  =  $T_A$  < 125 °C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                        | PARAMETER                    | TEST CONDITIONS               | MIN  | TYP   | MAX  | UNIT |

|------------------------|------------------------------|-------------------------------|------|-------|------|------|

| VCC BIAS SU            | JPPLY                        |                               |      |       |      |      |

| VCC <sub>SHUNT</sub>   | VCC shunt voltage (1)        | I <sub>VCC</sub> = 10 mA      | 22   | 24    | 26   | V    |

| I <sub>VCC(ULVO)</sub> | VCC current, UVLO            | VCC = 11.4 V prior to turn-on |      | 95    | 200  |      |

| I <sub>VCC(stby)</sub> | VCC current, disabled        | VSENSE = 0 V                  |      | 100   | 200  | μA   |

| I <sub>VCC(on)</sub>   | VCC current, enabled         | VSENSE = 2 V                  |      | 5     | 8    | mA   |

| UNDERVOLT              | AGE LOCKOUT (UVLO)           |                               |      |       |      |      |

| VCC <sub>ON</sub>      | VCC turn-on threshold        | VCC rising                    | 11.5 | 12.6  | 13.5 |      |

| VCC <sub>OFF</sub>     | VCC turn-off threshold       | VCC falling                   | 9.5  | 10.35 | 11.5 | V    |

|                        | UVLO Hysteresis              |                               | 1.85 | 2.15  | 2.45 |      |

| REFERENCE              |                              |                               |      |       |      |      |

| V <sub>REF</sub>       | VREF output voltage, no load | I <sub>VREF</sub> = 0 mA      | 5.82 | 6.00  | 6.18 | V    |

<sup>(1)</sup> Excessive VCC input voltage and current will damage the device. This clamp will not protect the device from an unregulated bias supply. If an unregulated bias supply is used, a series-connected Fixed Positive-Voltage Regulator such as the UA78L15A is recommended. See the Absolute Maximum Ratings table for the limits on VCC voltage, current, and junction temperature.

Product Folder Links: UCC28063A

# **Electrical Characteristics (continued)**

At VCC = 16 V, AGND = PGND = 0 V, VINAC = 3 V, VSENSE = 6 V, HVSEN = 3 V, PHB = 5 V,  $R_{TSET}$  = 133 k $\Omega$ , all voltages are with respect to GND, all outputs unloaded, -40 °C <  $T_J$  =  $T_A$  < 125 °C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                       | PARAMETER                                                                   | TEST CONDITIONS                                        | MIN    | TYP          | MAX    | UNIT |

|-----------------------|-----------------------------------------------------------------------------|--------------------------------------------------------|--------|--------------|--------|------|

|                       | VREF change with load                                                       | 0 mA ≤ I <sub>VREF</sub> ≤ −2 mA                       |        | -1           | -6     | .,   |

|                       | VREF change with VCC                                                        | 12 V ≤ VCC ≤ 20 V                                      |        | 2            | 10     | mV   |

| ERROR AMPLI           | FIER                                                                        |                                                        |        |              |        |      |

| VSENSEreg25           | VSENSE input regulation voltage                                             | T <sub>A</sub> = 25 °C                                 | 5.85   | 6            | 6.15   | V    |

| VSENSEreg             | VSENSE input regulation voltage                                             |                                                        | 5.82   | 6            | 6.18   | V    |

| I <sub>VSENSE</sub>   | VSENSE input bias current                                                   | In regulation                                          | 50     | 100          | 150    | nA   |

| V <sub>ENAB</sub>     | VSENSE enable threshold, rising                                             |                                                        | 1.15   | 1.25         | 1.35   |      |

|                       | VSENSE enable hysteresis                                                    |                                                        | 0.02   | 0.07         | 0.15   | V    |

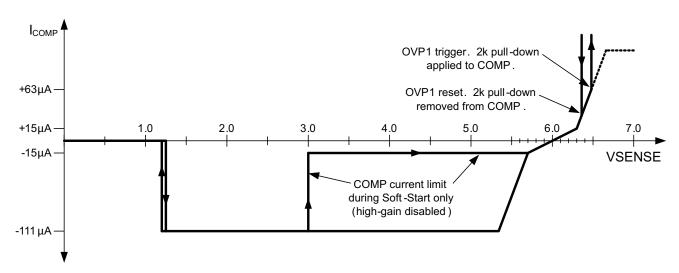

| V <sub>COMPCLMP</sub> | COMP high voltage, clamped                                                  | VSENSE = VSENSEreg - 0.3 V                             | 4.70   | 4.95         | 5.10   |      |

|                       | COMP low voltage, saturated                                                 | VSENSE = VSENSEreg + 0.3 V                             |        | 0.03         | 0.125  |      |

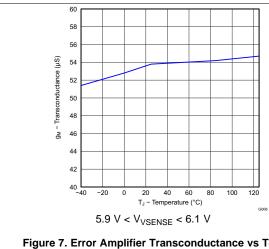

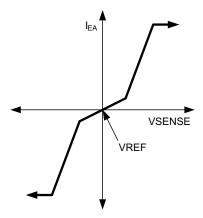

| 9м                    | VSENSE to COMP transconductance, small signal                               | 0.99(VSENSEreg) < VSENSE < 1.01(VSENSEreg), COMP = 3 V | 40     | 55           | 70     | μS   |

|                       | VSENSE high-going threshold<br>to enable COMP large signal<br>gain, percent | Relative to VSENSEreg, COMP = 3 V                      | 3.25%  | 5%           | 6.75%  |      |

|                       | VSENSE low-going threshold to enable COMP large signal gain, percent        | Relative to VSENSEreg, COMP = 3 V                      | -3.25% | <b>-</b> 5%  | -6.75% |      |

|                       | VSENSE to COMP transconductance, large signal                               | VSENSE = VSENSEreg - 0.4 V ,<br>COMP = 3 V             | 210    | 290          | 370    | 0    |

|                       | VSENSE to COMP transconductance, large signal                               | VSENSE = VSENSEreg + 0.4 V,<br>COMP = 3 V              | 210    | 290          | 370    | μS   |

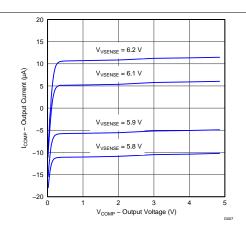

|                       | COMP maximum source current                                                 | VSENSE = 5 V, COMP = 3 V                               | -80    | <b>-</b> 125 | -170   | μΑ   |

| R <sub>COMPDCHG</sub> | COMP discharge resistance                                                   | HVSEN = 5.2 V, COMP = 3 V                              | 1.6    | 2            | 2.4    | kΩ   |

| I <sub>DODCHG</sub>   | COMP discharge current during Dropout                                       | VSENSE = 5 V, VINAC = 0.3 V                            | 3.2    | 4            | 4.8    | μΑ   |

| $V_{LOW\_OV}$         | VSENSE over-voltage threshold, rising                                       | Relative to VSENSEreg                                  | 7%     | 8%           | 10%    |      |

|                       | VSENSE over-voltage hysteresis                                              | Relative to V <sub>LOW_OV</sub>                        | -1.5%  | -2%          | -3%    |      |

| $V_{HIGH\_OV}$        | VSENSE 2nd over-voltage threshold, rising                                   | Relative to VSENSEreg                                  | 10.5%  | 11.3%        | 14%    |      |

| SOFT START            |                                                                             |                                                        |        |              |        |      |

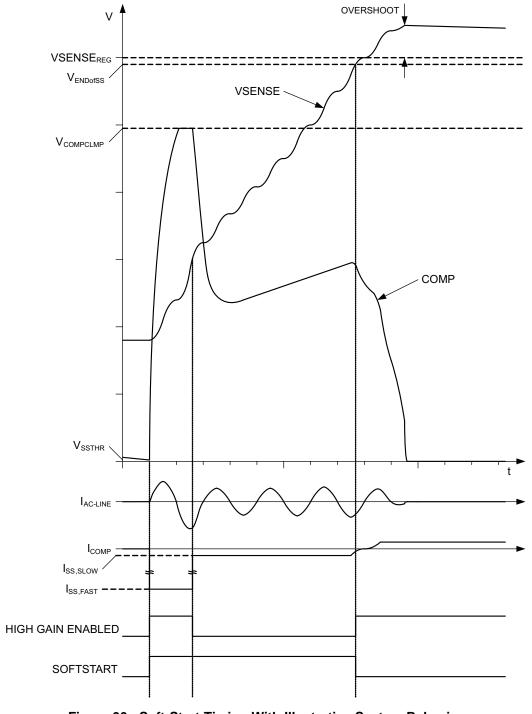

| $V_{SSTHR}$           | COMP Soft-Start threshold, falling                                          | VSENSE = 1.5 V                                         | 15     | 23           | 30     | mV   |

| I <sub>SS,FAST</sub>  | COMP Soft-Start current, fast                                               | SS-state, V <sub>ENAB</sub> < VSENSE < VREF/2          | -80    | -125         | -170   | μ.Λ  |

| I <sub>SS,SLOW</sub>  | COMP Soft-Start current, slow                                               | SS-state, VREF/2 < VSENSE < 0.88VREF                   | -11.5  | -16          | -20    | μA   |

| K <sub>EOSS</sub>     | VSENSE End-of-Soft-Start threshold factor                                   | Percent of VSENSEreg                                   | 96.5%  | 98.3%        | 99.8%  |      |

| OUTPUT MONI           | TORING                                                                      |                                                        |        |              |        |      |

| V <sub>PWMCNTL</sub>  | HVSEN threshold to PWMCNTL                                                  | HVSEN rising                                           | 2.35   | 2.50         | 2.65   | V    |

| I <sub>HVSEN</sub>    | HVSEN input bias current, high                                              | HVSEN = 3 V                                            |        | ±0.03        | ±0.5   | -    |

| I <sub>HV_HYS</sub>   | HVSEN hysteresis bias current, low                                          | HVSEN = 2 V                                            | 9.2    | 11.4         | 14     | μΑ   |

Submit Documentation Feedback

Copyright © 2014–2016, Texas Instruments Incorporated

# **Electrical Characteristics (continued)**

At VCC = 16 V, AGND = PGND = 0 V, VINAC = 3 V, VSENSE = 6 V, HVSEN = 3 V, PHB = 5 V,  $R_{TSET}$  = 133 k $\Omega$ , all voltages are with respect to GND, all outputs unloaded, -40 °C <  $T_J$  =  $T_A$  < 125 °C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                           | PARAMETER                                              | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MIN    | TYP    | MAX                                                                                                        | UNIT |

|---------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|------------------------------------------------------------------------------------------------------------|------|

| V <sub>HV_OV_FLT</sub>    | HVSEN threshold to over-<br>voltage fault              | HVSEN rising                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4.64   | 4.87   | 5.1                                                                                                        |      |

| V <sub>HV_OV_CLR</sub>    | HVSEN threshold to over-<br>voltage clear              | HVSEN falling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.45   | 4.67   | 4.8                                                                                                        |      |

| V <sub>COMP_PHFOFF</sub>  | Phase Fail monitoring-disable threshold                | COMP falling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.21   | 0.225  | 0.25                                                                                                       | V    |

| V <sub>COMP_PHFHYS</sub>  | Phase Fail monitoring hysteresis                       | COMP rising                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        | 0.051  |                                                                                                            |      |

|                           | PWMCNTL output voltage low                             | HVSEN = 3 V, I <sub>PWMCNTL</sub> = 5 mA,<br>COMP = 0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        | 0.2    | 0.5                                                                                                        |      |

| t <sub>PHFDLY</sub>       | Phase Fail filter time to PWMCNTL high                 | PHB = 5 V, ZCDA switching,<br>ZCDB = 0.5 V, COMP = 3 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7.9    | 12     | 17                                                                                                         | ms   |

| I <sub>PWMCNTL_LEAK</sub> | PWMCNTL leakage current, high                          | HVSEN = 2 V, PWMCNTL = 15 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        | ±0.03  | ±0.5                                                                                                       | μΑ   |

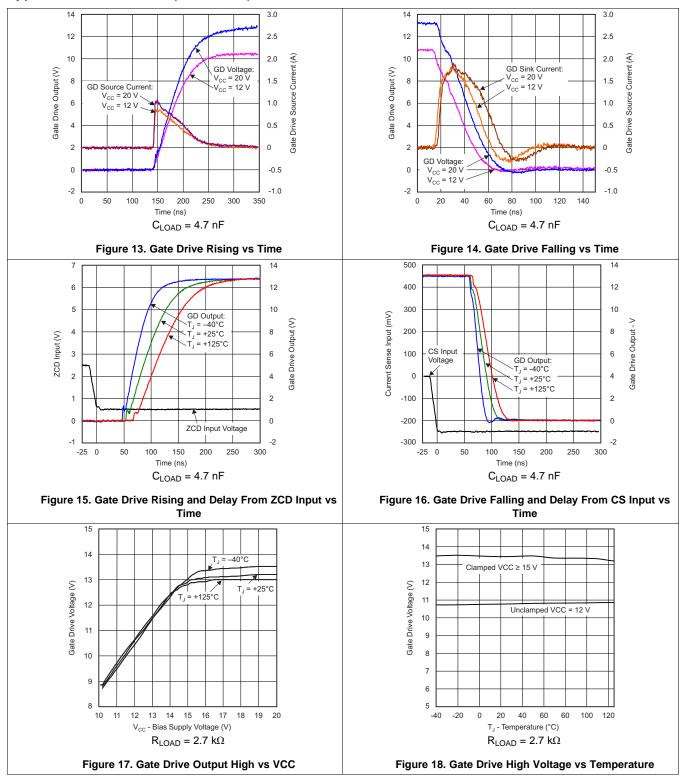

| GATE DRIVE <sup>(2</sup>  | )                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |        |                                                                                                            |      |

|                           | GDA, GDB output voltage, high                          | I <sub>GDA</sub> , I <sub>GDB</sub> = −100 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11.5   | 12.4   | 15                                                                                                         | V    |

|                           | GDA, GDB on-resistance, high                           | I <sub>GDA</sub> , I <sub>GDB</sub> = −100 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        | 8.8    | 14                                                                                                         | Ω    |

|                           | GDA, GDB output voltage, low                           | I <sub>GDA</sub> , I <sub>GDB</sub> = 100 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        | 0.18   | 0.32                                                                                                       | V    |

|                           | GDA, GDB on-resistance, low                            | I <sub>GDA</sub> , I <sub>GDB</sub> = 100 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        | 2      | 3.2                                                                                                        | Ω    |

|                           | GDA, GDB output voltage high, clamped                  | VCC = 20 V, I <sub>GDA</sub> , I <sub>GDB</sub> = -5 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12     | 13.5   | 15                                                                                                         |      |

|                           | GDA, GDB output voltage high, low VCC                  | $VCC = 12 \text{ V}, I_{GDA}, I_{GDB} = -5 \text{ mA}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10     | 10.5   | 11.5                                                                                                       | V    |

|                           | Rise time                                              | 1 V to 9 V, C <sub>LOAD</sub> = 1 nF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        | 18     | 30                                                                                                         |      |

|                           | Fall time                                              | 9 V to 1 V, C <sub>LOAD</sub> = 1 nF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        | 12     | 25                                                                                                         | ns   |

|                           | GDA, GDB output voltage, UVLO                          | VCC = 3.0 V, I <sub>GDA</sub> , I <sub>GDB</sub> = 2.5 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        | 100    | 200                                                                                                        | mV   |

| ZERO CURREI               | NT DETECTOR                                            | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | II.    |        |                                                                                                            |      |

|                           | ZCDA, ZCDB voltage threshold, falling                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.8    | 1      | 1.2                                                                                                        |      |

|                           | ZCDA, ZCDB voltage threshold, rising                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.5    | 1.7    | 1.9                                                                                                        | V    |

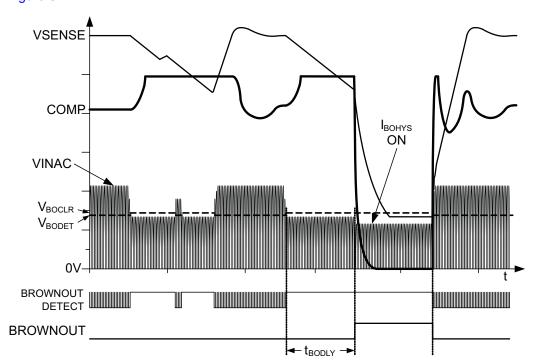

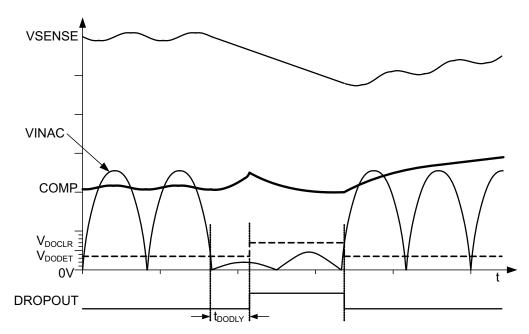

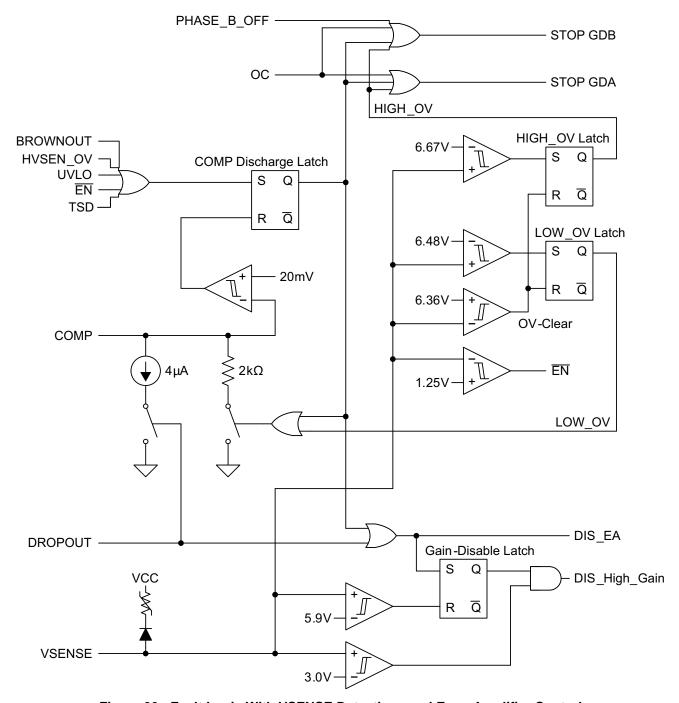

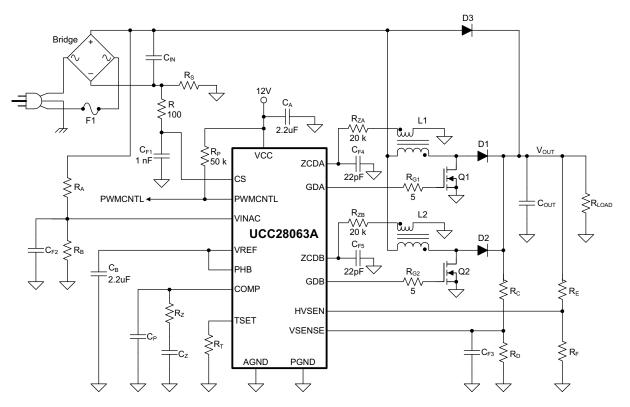

|                           | ZCDA, ZCDB clamp, high                                 | $I_{ZCDA}$ = +2 mA, $I_{ZCDB}$ = +2 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2.6    | 3      | 3.4                                                                                                        |      |