## **Single IGBT Gate Driver**

The MC33153 is specifically designed as an IGBT driver for high power applications that include ac induction motor control, brushless dc motor control and uninterruptable power supplies. Although designed for driving discrete and module IGBTs, this device offers a cost effective solution for driving power MOSFETs and Bipolar Transistors. Device protection features include the choice of desaturation or overcurrent sensing and undervoltage detection. These devices are available in dual-in-line and surface mount packages.

#### **Features**

- High Current Output Stage: 1.0 A Source/2.0 A Sink

- Protection Circuits for Both Conventional and Sense IGBTs

- Programmable Fault Blanking Time

- Protection against Overcurrent and Short Circuit

- Undervoltage Lockout Optimized for IGBT's

- Negative Gate Drive Capability

- Cost Effectively Drives Power MOSFETs and Bipolar Transistors

- This is a Pb-Free and Halide-Free Device

This device contains 133 active transistors.

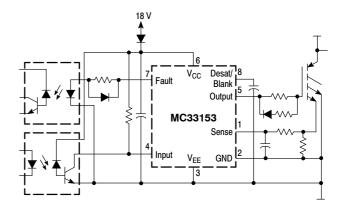

Figure 1. Representative Block Diagram

1

#### ON Semiconductor®

http://onsemi.com

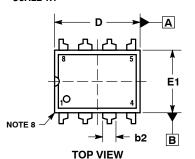

#### MARKING DIAGRAMS

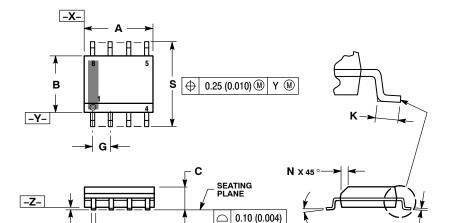

SOIC-8 D SUFFIX CASE 751

PDIP-8 P SUFFIX CASE 626

A = Assembly Location

L, WL = Wafer Lot Y, YY = Year W, WW = Work Week

■ or G = Pb-Free Package

(Note: Microdot may be in either location)

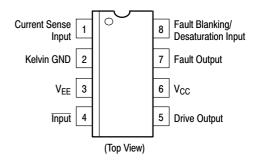

#### PIN CONNECTIONS

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 12 of this data sheet.

#### **MAXIMUM RATINGS**

| Rating                                                                                                                                                                                                                                                                                     | Symbol                                                                   | Value                                   | Unit                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------|------------------------|

| Power Supply Voltage V <sub>CC</sub> to V <sub>EE</sub> Kelvin Ground to V <sub>EE</sub> (Note 1)                                                                                                                                                                                          | V <sub>CC</sub> - V <sub>EE</sub><br>KGND - V <sub>EE</sub>              | 20                                      | V                      |

| Logic Input                                                                                                                                                                                                                                                                                | V <sub>in</sub>                                                          | V <sub>EE</sub> -0.3 to V <sub>CC</sub> | V                      |

| Current Sense Input                                                                                                                                                                                                                                                                        | V <sub>S</sub>                                                           | -0.3 to V <sub>CC</sub>                 | V                      |

| Blanking/Desaturation Input                                                                                                                                                                                                                                                                | V <sub>BD</sub>                                                          | -0.3 to V <sub>CC</sub>                 | V                      |

| Gate Drive Output Source Current Sink Current Diode Clamp Current                                                                                                                                                                                                                          | Io                                                                       | 1.0<br>2.0<br>1.0                       | A                      |

| Fault Output Source Current Sink Current                                                                                                                                                                                                                                                   | lFO                                                                      | 25<br>10                                | mA                     |

| Power Dissipation and Thermal Characteristics D Suffix SO-8 Package, Case 751 Maximum Power Dissipation @ T <sub>A</sub> = 50°C Thermal Resistance, Junction-to-Air P Suffix DIP-8 Package, Case 626 Maximum Power Dissipation @ T <sub>A</sub> = 50°C Thermal Resistance, Junction-to-Air | P <sub>D</sub><br>R <sub>θJA</sub><br>P <sub>D</sub><br>R <sub>θJA</sub> | 0.56<br>180<br>1.0<br>100               | W<br>°C/W<br>W<br>°C/W |

| Operating Junction Temperature                                                                                                                                                                                                                                                             | TJ                                                                       | +150                                    | °C                     |

| Operating Ambient Temperature                                                                                                                                                                                                                                                              | T <sub>A</sub>                                                           | -40 to +105                             | °C                     |

| Storage Temperature Range                                                                                                                                                                                                                                                                  | T <sub>stg</sub>                                                         | -65 to +150                             | °C                     |

| Electrostatic Discharge Sensitivity (ESD) (Note 2)<br>Human Body Model (HBM)<br>Machine Model (MM)<br>Charged Device Model (CDM)                                                                                                                                                           | ESD                                                                      | 2500<br>250<br>1500                     | V                      |

NOTE: ESD data available upon request.

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect

Kelvin Ground must always be between V<sub>EE</sub> and V<sub>CC</sub>.

ESD protection per JEDEC Standard JESD22–A114–F for HBM per JEDEC Standard JESD22–A115–A for MM

per JEDEC Standard JESD22-C101D for CDM.

**ELECTRICAL CHARACTERISTICS** ( $V_{CC}$  = 15 V,  $V_{EE}$  = 0 V, Kelvin GND connected to  $V_{EE}$ . For typical values  $T_A$  = 25°C, for min/max values T<sub>A</sub> is the operating ambient temperature range that applies (Note 3), unless otherwise noted.)

| Characteristic                                                                                       | Symbol                             | Min      | Тур          | Max        | Unit |

|------------------------------------------------------------------------------------------------------|------------------------------------|----------|--------------|------------|------|

| LOGIC INPUT                                                                                          |                                    |          |              |            |      |

| Input Threshold Voltage High State (Logic 1) Low State (Logic 0)                                     | V <sub>IH</sub><br>V <sub>IL</sub> | _<br>1.2 | 2.70<br>2.30 | 3.2        | V    |

| Input Current High State ( $V_{IH} = 3.0 \text{ V}$ ) Low State ( $V_{IL} = 1.2 \text{ V}$ )         | I <sub>IH</sub><br>I <sub>IL</sub> | -<br>-   | 130<br>50    | 500<br>100 | μΑ   |

| DRIVE OUTPUT                                                                                         |                                    |          |              |            |      |

| Output Voltage<br>Low State (I <sub>Sink</sub> = 1.0 A)<br>High State (I <sub>Source</sub> = 500 mA) | V <sub>OL</sub><br>V <sub>OH</sub> | _<br>12  | 2.0<br>13.9  | 2.5<br>-   | V    |

| Output Pull-Down Resistor                                                                            | R <sub>PD</sub>                    | _        | 100          | 200        | kΩ   |

| FAULT OUTPUT                                                                                         | •                                  | •        | •            | •          |      |

| Output Voltage Low State (I <sub>Sink</sub> = 5.0 mA) High State (I <sub>Source</sub> = 20 mA)       | V <sub>FL</sub><br>V <sub>FH</sub> | _<br>12  | 0.2<br>13.3  | 1.0        | V    |

<sup>3.</sup> Low duty cycle pulse techniques are used during test to maintain the junction temperature as close to ambient as possible.  $T_{low} = -40^{\circ}\text{C}$  for MC33153  $T_{high} = +105^{\circ}\text{C}$  for MC33153

**ELECTRICAL CHARACTERISTICS** (continued) ( $V_{CC}$  = 15 V,  $V_{EE}$  = 0 V, Kelvin GND connected to  $V_{EE}$ . For typical values  $T_A$  = 25°C, for min/max values  $T_A$  is the operating ambient temperature range that applies (Note 4), unless otherwise noted.)

|                                                                    | Characteristic                                                                        | Symbol                                    | Min    | Тур        | Max        | Unit |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------|--------|------------|------------|------|

| SWITCHING CHARA                                                    | ACTERISTICS                                                                           | •                                         | •      | •          |            |      |

| Propagation Delay (<br>Logic Input to Dri<br>Logic Input to Dri    |                                                                                       | tPLH(in/out)<br>tPHL (in/out)             | _<br>_ | 80<br>120  | 300<br>300 | ns   |

| Drive Output Rise Ti                                               | me (10% to 90%) C <sub>L</sub> = 1.0 nF                                               | t <sub>r</sub>                            | _      | 17         | 55         | ns   |

| Drive Output Fall Tin                                              | ne (90% to 10%) C <sub>L</sub> = 1.0 nF                                               | t <sub>f</sub>                            | _      | 17         | 55         | ns   |

| Propagation Delay                                                  | Current Sense Input to Drive Output Fault Blanking/Desaturation Input to Drive Output | t <sub>P(OC)</sub><br>t <sub>P(FLT)</sub> | -      | 0.3        | 1.0        | μs   |

| UVLO                                                               |                                                                                       |                                           |        |            |            |      |

| Startup Voltage                                                    |                                                                                       | V <sub>CC start</sub>                     | 11.3   | 12         | 12.6       | V    |

| Disable Voltage                                                    |                                                                                       | V <sub>CC dis</sub>                       | 10.4   | 11         | 11.7       | V    |

| COMPARATORS                                                        |                                                                                       | •                                         | •      | •          | •          | •    |

| Overcurrent Thresho                                                | old Voltage (V <sub>Pin8</sub> > 7.0 V)                                               | V <sub>SOC</sub>                          | 50     | 65         | 80         | mV   |

| Short Circuit Threshold Voltage (V <sub>Pin8</sub> > 7.0 V)        |                                                                                       | V <sub>SSC</sub>                          | 100    | 130        | 160        | mV   |

| Fault Blanking/Desaturation Threshold (V <sub>Pin1</sub> > 100 mV) |                                                                                       | V <sub>th(FLT)</sub>                      | 6.0    | 6.5        | 7.0        | V    |

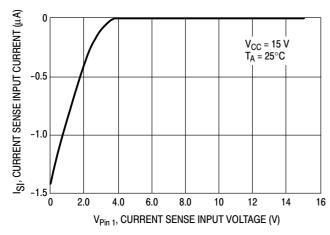

| Current Sense Input Current (V <sub>SI</sub> = 0 V)                |                                                                                       | I <sub>SI</sub>                           | _      | -1.4       | -10        | μΑ   |

| FAULT BLANKING/                                                    | DESATURATION INPUT                                                                    |                                           |        |            |            |      |

| Current Source (V <sub>Pir</sub>                                   | <sub>18</sub> = 0 V, V <sub>Pin4</sub> = 0 V)                                         | I <sub>chg</sub>                          | -200   | -270       | -300       | μΑ   |

| Discharge Current (\                                               | Discharge Current (V <sub>Pin8</sub> = 15 V, V <sub>Pin4</sub> = 5.0 V)               |                                           | 1.0    | 2.5        | -          | mA   |

| TOTAL DEVICE                                                       |                                                                                       |                                           |        |            |            |      |

|                                                                    | nt<br>: V <sub>CC</sub> , Output Open)<br>1.0 nF, f = 20 kHz)                         | I <sub>CC</sub>                           | _<br>_ | 7.2<br>7.9 | 14<br>20   | mA   |

Low duty cycle pulse techniques are used during test to maintain the junction temperature as close to ambient as possible.

T<sub>low</sub> = -40°C for MC33153

T<sub>high</sub> = +105°C for MC33153

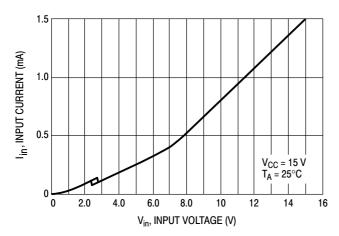

Figure 2. Input Current versus Input Voltage

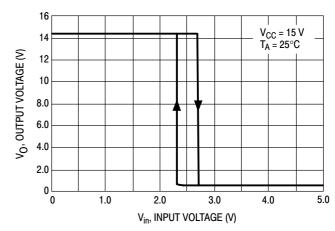

Figure 3. Output Voltage versus Input Voltage

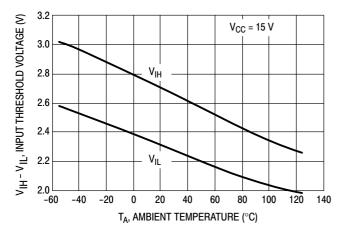

Figure 4. Input Threshold Voltage versus Temperature

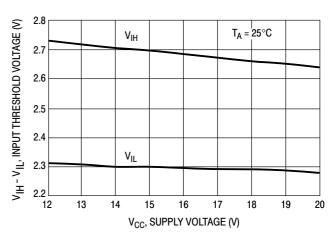

Figure 5. Input Threshold Voltage versus Supply Voltage

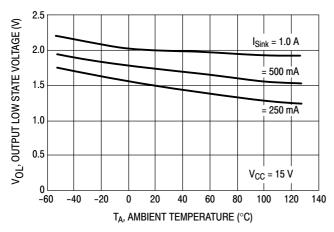

Figure 6. Drive Output Low State Voltage versus Temperature

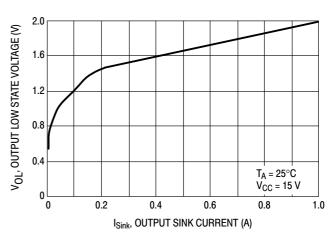

Figure 7. Drive Output Low State Voltage versus Sink Current

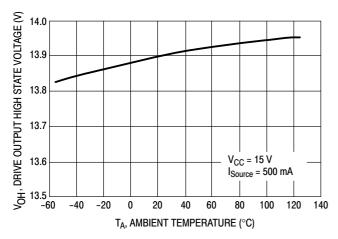

Figure 8. Drive Output High State Voltage versus Temperature

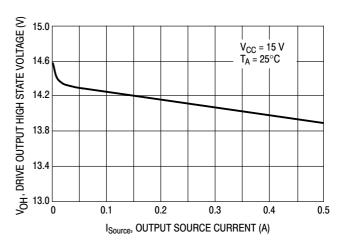

Figure 9. Drive Output High State Voltage versus Source Current

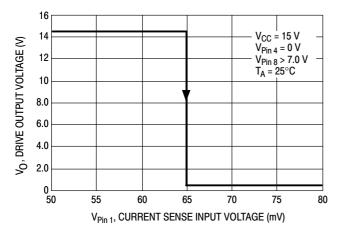

Figure 10. Drive Output Voltage versus Current Sense Input Voltage

Figure 11. Fault Output Voltage versus Current Sense Input Voltage

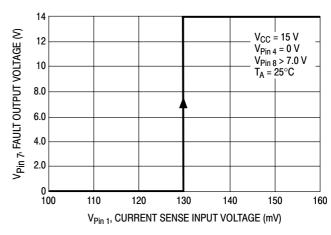

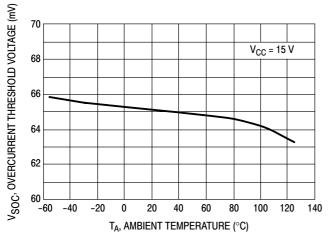

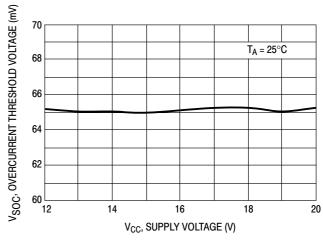

Figure 12. Overcurrent Protection Threshold Voltage versus Temperature

Figure 13. Overcurrent Protection Threshold Voltage versus Supply Voltage

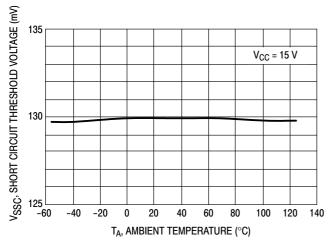

Figure 14. Short Circuit Comparator Threshold Voltage versus Temperature

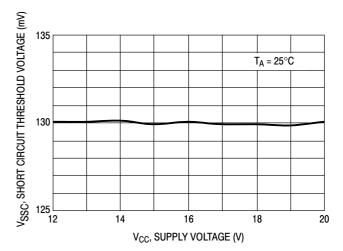

Figure 15. Short Circuit Comparator Threshold Voltage versus Supply Voltage

Figure 16. Current Sense Input Current versus Voltage

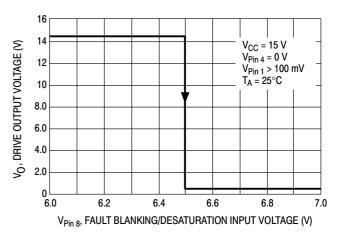

Figure 17. Drive Output Voltage versus Fault Blanking/Desaturation Input Voltage

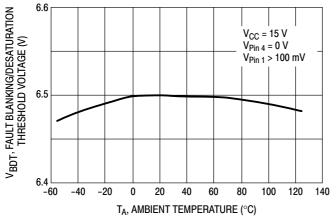

Figure 18. Fault Blanking/Desaturation Comparator Threshold Voltage versus Temperature

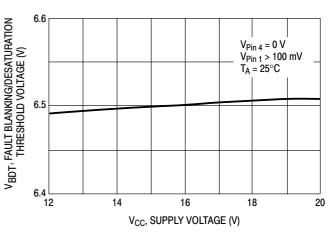

Figure 19. Fault Blanking/Desaturation Comparator Threshold Voltage versus Supply Voltage

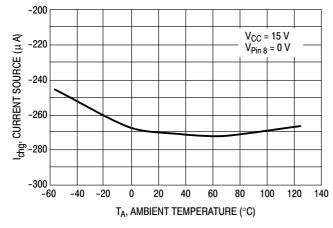

Figure 20. Fault Blanking/Desaturation Current Source versus Temperature

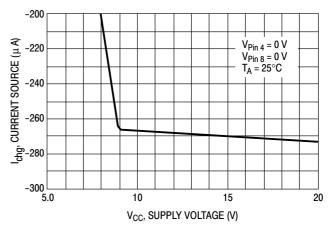

Figure 21. Fault Blanking/Desaturation Current Source versus Supply Voltage

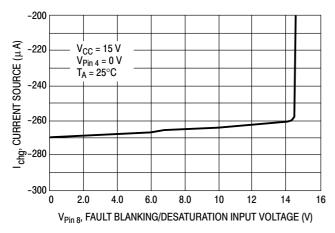

Figure 22. Fault Blanking/Desaturation Current Source versus Input Voltage

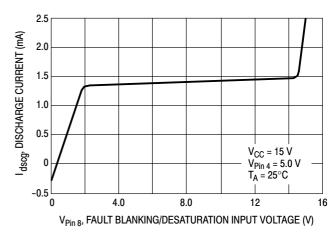

Figure 23. Fault Blanking/Desaturation Discharge Current versus Input Voltage

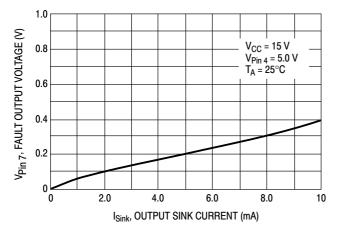

Figure 24. Fault Output Low State Voltage versus Sink Current

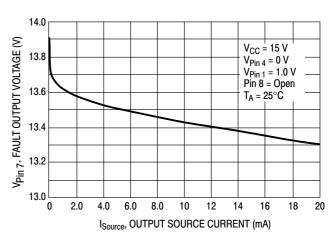

Figure 25. Fault Output High State Voltage versus Source Current

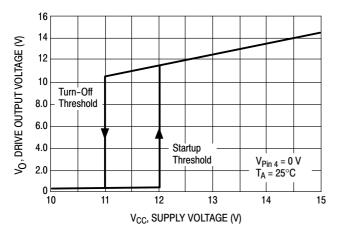

Figure 26. Drive Output Voltage versus Supply Voltage

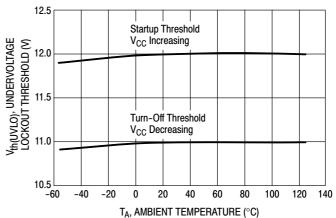

Figure 27. UVLO Thresholds versus Temperature

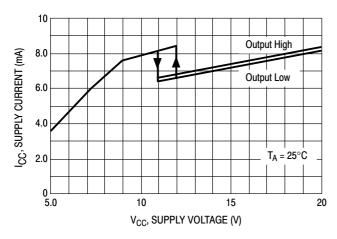

Figure 28. Supply Current versus Supply Voltage

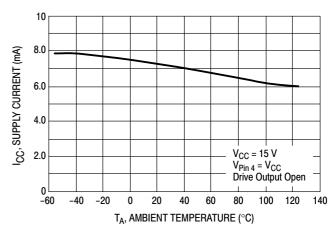

Figure 29. Supply Current versus Temperature

Figure 30. Supply Current versus Input Frequency

#### **OPERATING DESCRIPTION**

#### **GATE DRIVE**

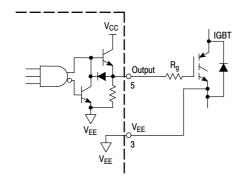

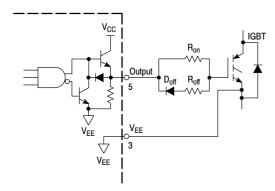

#### **Controlling Switching Times**

The most important design aspect of an IGBT gate drive is optimization of the switching characteristics. The switching characteristics are especially important in motor control applications in which PWM transistors are used in a bridge configuration. In these applications, the gate drive circuit components should be selected to optimize turn-on, turn-off and off-state impedance. A single resistor may be used to control both turn-on and turn-off as shown in Figure 31. However, the resistor value selected must be a compromise in turn-on abruptness and turn-off losses. Using a single resistor is normally suitable only for very low frequency PWM. An optimized gate drive output stage is shown in Figure 32. This circuit allows turn-on and turn-off to be optimized separately. The turn-on resistor, Ron, provides control over the IGBT turn-on speed. In motor control circuits, the resistor sets the turn-on di/dt that controls how fast the free-wheel diode is cleared. The interaction of the IGBT and free-wheeling diode determines the turn–on dv/dt. Excessive turn–on dv/dt is a common problem in half–bridge circuits. The turn–off resistor,  $R_{\rm off}$ , controls the turn–off speed and ensures that the IGBT remains off under commutation stresses. Turn–off is critical to obtain low switching losses. While IGBTs exhibit a fixed minimum loss due to minority carrier recombination, a slow gate drive will dominate the turn–off losses. This is particularly true for fast IGBTs. It is also possible to turn–off an IGBT too fast. Excessive turn–off speed will result in large overshoot voltages. Normally, the turn–off resistor is a small fraction of the turn–on resistor.

The MC33153 contains a bipolar totem pole output stage that is capable of sourcing 1.0 amp and sinking 2.0 amps peak. This output also contains a pull down resistor to ensure that the IGBT is off whenever there is insufficient  $V_{\rm CC}$  to the MC33153.

In a PWM inverter, IGBTs are used in a half-bridge configuration. Thus, at least one device is always off. While

the IGBT is in the off-state, it will be subjected to changes in voltage caused by the other devices. This is particularly a problem when the opposite transistor turns on.

When the lower device is turned on, clearing the upper diode, the turn-on dv/dt of the lower device appears across the collector emitter of the upper device. To eliminate shoot-through currents, it is necessary to provide a low sink impedance to the device that is in the off-state. In most applications the turn-off resistor can be made small enough to hold off the device that is under commutation without causing excessively fast turn-off speeds.

Figure 31. Using a Single Gate Resistor

Figure 32. Using Separate Resistors for Turn-On and Turn-Off

A negative bias voltage can be used to drive the IGBT into the off-state. This is a practice carried over from bipolar Darlington drives and is generally not required for IGBTs. However, a negative bias will reduce the possibility of shoot-through. The MC33153 has separate pins for  $V_{\rm EE}$  and Kelvin Ground. This permits operation using a +15/–5.0 V supply.

# INTERFACING WITH OPTOISOLATORS Isolated Input

The MC33153 may be used with an optically isolated input. The optoisolator can be used to provide level shifting, and if desired, isolation from ac line voltages. An optoisolator with a very high dv/dt capability should be used, such as the Hewlett Packard HCPL4053. The IGBT gate turn-on resistor should be set large enough to ensure

that the opto's dv/dt capability is not exceeded. Like most optoisolators, the HCPL4053 has an active low open-collector output. Thus, when the LED is on, the output will be low. The MC33153 has an inverting input pin to interface directly with an optoisolator using a pullup resistor. The input may also be interfaced directly to 5.0 V CMOS logic or a microcontroller.

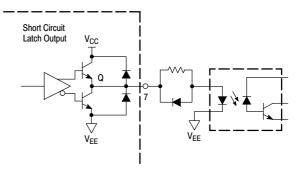

#### **Optoisolator Output Fault**

The MC33153 has an active high fault output. The fault output may be easily interfaced to an optoisolator. While it is important that all faults are properly reported, it is equally important that no false signals are propagated. Again, a high dv/dt optoisolator should be used.

The LED drive provides a resistor programmable current of 10 to 20 mA when on, and provides a low impedance path when off. An active high output, resistor, and small signal diode provide an excellent LED driver. This circuit is shown in Figure 33.

Figure 33. Output Fault Optoisolator

#### UNDERVOLTAGE LOCKOUT

It is desirable to protect an IGBT from insufficient gate voltage. IGBTs require 15 V on the gate to achieve the rated on–voltage. At gate voltages below 13 V, the on–voltage increases dramatically, especially at higher currents. At very low gate voltages, below 10 V, the IGBT may operate in the linear region and quickly overheat. Many PWM motor drives use a bootstrap supply for the upper gate drive. The UVLO provides protection for the IGBT in case the bootstrap capacitor discharges.

The MC33153 will typically start up at about 12 V. The UVLO circuit has about 1.0 V of hysteresis and will disable the output if the supply voltage falls below about 11 V.

#### PROTECTION CIRCUITRY

#### **Desaturation Protection**

Bipolar Power circuits have commonly used what is known as "Desaturation Detection". This involves monitoring the collector voltage and turning off the device if this voltage rises above a certain limit. A bipolar transistor will only conduct a certain amount of current for a given base drive. When the base is overdriven, the device is in saturation. When the collector current rises above the knee, the device pulls out of saturation. The maximum current the device will conduct in the linear region is a function of the base current and the dc current gain (h<sub>FE</sub>) of the transistor.

The output characteristics of an IGBT are similar to a Bipolar device. However, the output current is a function of gate voltage instead of current. The maximum current depends on the gate voltage and the device type. IGBTs tend to have a very high transconductance and a much higher current density under a short circuit than a bipolar device. Motor control IGBTs are designed for a lower current density under shorted conditions and a longer short circuit survival time.

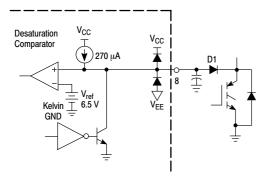

The best method for detecting desaturation is the use of a high voltage clamp diode and a comparator. The MC33153 has a Fault Blanking/Desaturation Comparator which senses the collector voltage and provides an output indicating when the device is not fully saturated. Diode D1 is an external high voltage diode with a rated voltage comparable to the power device. When the IGBT is "on" and saturated, D1 will pull down the voltage on the Fault Blanking/Desaturation Input. When the IGBT pulls out of saturation or is "off", the current source will pull up the input and trip the comparator. The comparator threshold is 6.5 V, allowing a maximum on–voltage of about 5.8 V.

A fault exists when the gate input is high and  $V_{CE}$  is greater than the maximum allowable  $V_{CE(sat)}$ . The output of the Desaturation Comparator is ANDed with the gate input signal and fed into the Short Circuit and Overcurrent Latches. The Overcurrent Latch will turn–off the IGBT for the remainder of the cycle when a fault is detected. When input goes high, both latches are reset. The reference voltage is tied to the Kelvin Ground instead of the  $V_{EE}$  to make the threshold independent of negative gate bias. Note that for proper operation of the Desaturation Comparator and the Fault Output, the Current Sense Input must be biased above the Overcurrent and Short Circuit Comparator thresholds. This can be accomplished by connecting Pin 1 to  $V_{CC}$ .

Figure 34. Desaturation Detection

The MC33153 also features a programmable fault blanking time. During turn-on, the IGBT must clear the opposing free-wheeling diode. The collector voltage will remain high until the diode is cleared. Once the diode has

been cleared, the voltage will come down quickly to the  $V_{CE(sat)}$  of the device. Following turn–on, there is normally considerable ringing on the collector due to the  $C_{OSS}$  capacitance of the IGBTs and the parasitic wiring inductance. The fault signal from the Desaturation Comparator must be blanked sufficiently to allow the diode to be cleared and the ringing to settle out.

The blanking function uses an NPN transistor to clamp the comparator input when the gate input is low. When the input is switched high, the clamp transistor will turn "off", allowing the internal current source to charge the blanking capacitor. The time required for the blanking capacitor to charge up from the on–voltage of the internal NPN transistor to the trip voltage of the comparator is the blanking time.

If a short circuit occurs after the IGBT is turned on and saturated, the delay time will be the time required for the current source to charge up the blanking capacitor from the  $V_{CE(sat)}$  level of the IGBT to the trip voltage of the comparator. Fault blanking can be disabled by leaving Pin 8 unconnected.

#### **Sense IGBT Protection**

Another approach to protecting the IGBTs is to sense the emitter current using a current shunt or Sense IGBTs. This method has the advantage of being able to use high gain IGBTs which do not have any inherent short circuit capability. Current sense IGBTs work as well as current sense MOSFETs in most circumstances. However, the basic problem of working with very low sense voltages still exists. Sense IGBTs sense current through the channel and are therefore linear with respect to the collector current. Because IGBTs have a very low incremental on–resistance, sense IGBTs behave much like low–on resistance current sense MOSFETs. The output voltage of a properly terminated sense IGBT is very low, normally less than 100 mV.

The sense IGBT approach requires fault blanking to prevent false tripping during turn-on. The sense IGBT also requires that the sense signal is ignored while the gate is low. This is because the mirror output normally produces large transient voltages during both turn-on and turn-off due to the collector to mirror capacitance. With non-sensing types of IGBTs, a low resistance current shunt (5.0 to 50 m $\Omega$ ) can be used to sense the emitter current. When the output is an actual short circuit, the inductance will be very low. Since the blanking circuit provides a fixed minimum on-time, the peak current under a short circuit can be very high. A short circuit discern function is implemented by the second comparator which has a higher trip voltage. The short circuit signal is latched and appears at the Fault Output. When a short circuit is detected, the IGBT should be turned-off for several milliseconds allowing it to cool down before it is turned back on. The sense circuit is very similar to the desaturation circuit. It is possible to build a combination circuit that provides protection for both Short Circuit capable IGBTs and Sense IGBTs.

#### APPLICATION INFORMATION

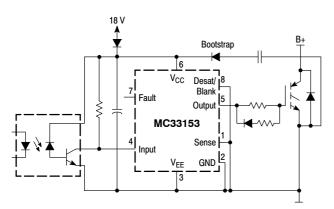

Figure 35 shows a basic IGBT driver application. When driven from an optoisolator, an input pull up resistor is required. This resistor value should be set to bias the output transistor at the desired current. A decoupling capacitor should be placed close to the IC to minimize switching noise.

A bootstrap diode may be used for a floating supply. If the protection features are not required, then both the Fault Blanking/Desaturation and Current Sense Inputs should both be connected to the Kelvin Ground (Pin 2). When used with a single supply, the Kelvin Ground and  $V_{\rm EE}$  pins should be connected together. Separate gate resistors are recommended to optimize the turn-on and turn-off drive.

Figure 35. Basic Application

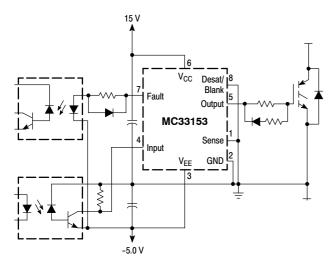

Figure 36. Dual Supply Application

When used in a dual supply application as in Figure 36, the Kelvin Ground should be connected to the emitter of the IGBT. If the protection features are not used, then both the Fault Blanking/Desaturation and the Current Sense Inputs should be connected to Ground. The input optoisolator should always be referenced to  $V_{\rm FF}$ .

If desaturation protection is desired, a high voltage diode is connected to the Fault Blanking/Desaturation pin. The

blanking capacitor should be connected from the Desaturation pin to the  $V_{\rm EE}$  pin. If a dual supply is used, the blanking capacitor should be connected to the Kelvin Ground. The Current Sense Input should be tied high because the two comparator outputs are ANDed together. Although the reverse voltage on collector of the IGBT is clamped to the emitter by the free–wheeling diode, there is normally considerable inductance within the package itself. A small resistor in series with the diode can be used to protect the IC from reverse voltage transients.

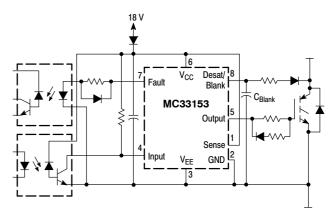

Figure 37. Desaturation Application

When using sense IGBTs or a sense resistor, the sense voltage is applied to the Current Sense Input. The sense trip voltages are referenced to the Kelvin Ground pin. The sense voltage is very small, typically about 65 mV, and sensitive to noise. Therefore, the sense and ground return conductors should be routed as a differential pair. An RC filter is useful in filtering any high frequency noise. A blanking capacitor is connected from the blanking pin to  $V_{\rm EE}$ . The stray capacitance on the blanking pin provides a very small level of blanking if left open. The blanking pin should not be grounded when using current sensing, that would disable the sense. The blanking pin should never be tied high, that would short out the clamp transistor.

Figure 38. Sense IGBT Application

#### **ORDERING INFORMATION**

| Device      | Operating Temperature Range                          | Package             | Shipping <sup>†</sup> |

|-------------|------------------------------------------------------|---------------------|-----------------------|

| MC33153DG   |                                                      | SOIC-8<br>(Pb-Free) | 98 Units / Rail       |

| MC33153DR2G | $T_A = -40^{\circ} \text{ to } +105^{\circ}\text{C}$ | SOIC-8<br>(Pb-Free) | 1000 / Tape & Reel    |

| MC33153PG   |                                                      | PDIP-8<br>(Pb-Free) | 50 Units / Rail       |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

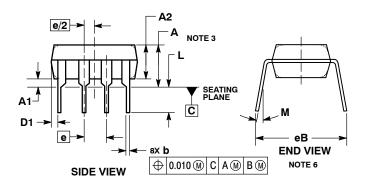

PDIP-8 CASE 626-05 **ISSUE P**

**DATE 22 APR 2015**

NOTE 5

STYLE 1: PIN 1. AC IN 2. DC + IN 3. DC - IN 4. AC IN

5. GROUND 6. OUTPUT

7. AUXILIARY 8. V<sub>CC</sub>

#### NOTES

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- CONTROLLING DIMENSION: INCHES.

DIMENSIONS A, A1 AND L ARE MEASURED WITH THE PACK-

- AGE SEATED IN JEDEC SEATING PLANE GAUGE GS-3.

DIMENSIONS D, D1 AND E1 DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS ARE NOT TO EXCEED 0.10 INCH.

- DIMENSION E IS MEASURED AT A POINT 0.015 BELOW DATUM PLANE H WITH THE LEADS CONSTRAINED PERPENDICULAR TO DATUM C.

- 6. DIMENSION eB IS MEASURED AT THE LEAD TIPS WITH THE

- DATUM PLANE H IS COINCIDENT WITH THE BOTTOM OF THE LEADS, WHERE THE LEADS EXIT THE BODY.

- 8. PACKAGE CONTOUR IS OPTIONAL (ROUNDED OR SQUARE CORNERS).

|     | INCHES    |       | MILLIM | ETERS |

|-----|-----------|-------|--------|-------|

| DIM | MIN       | MAX   | MIN    | MAX   |

| Α   |           | 0.210 |        | 5.33  |

| A1  | 0.015     |       | 0.38   |       |

| A2  | 0.115     | 0.195 | 2.92   | 4.95  |

| b   | 0.014     | 0.022 | 0.35   | 0.56  |

| b2  | 0.060 TYP |       | 1.52   | TYP   |

| С   | 0.008     | 0.014 | 0.20   | 0.36  |

| D   | 0.355     | 0.400 | 9.02   | 10.16 |

| D1  | 0.005     |       | 0.13   |       |

| Е   | 0.300     | 0.325 | 7.62   | 8.26  |

| E1  | 0.240     | 0.280 | 6.10   | 7.11  |

| е   | 0.100     | BSC   | 2.54   | BSC   |

| eВ  |           | 0.430 |        | 10.92 |

| L   | 0.115     | 0.150 | 2.92   | 3.81  |

| M   |           | 10°   |        | 10°   |

#### **GENERIC MARKING DIAGRAM\***

XXXX = Specific Device Code = Assembly Location WL = Wafer Lot

YY = Year WW = Work Week = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "■", may or may not be present. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER: | 98ASB42420B | Electronic versions are uncontrolled except when accessed directly from the Document Reposito<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | PDIP-8      |                                                                                                                                                                                  | PAGE 1 OF 1 |  |

onsemi and Onsemi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries, onsemi reserves the right to make changes without further notice to any products herein. **onsemi** makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

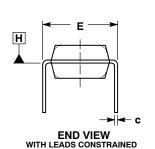

#### SOIC-8 NB CASE 751-07 **ISSUE AK**

**DATE 16 FEB 2011**

XS

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

|     | MILLIMETERS |          | INC   | HES   |

|-----|-------------|----------|-------|-------|

| DIM | MIN         | MAX      | MIN   | MAX   |

| Α   | 4.80        | 5.00     | 0.189 | 0.197 |

| В   | 3.80        | 4.00     | 0.150 | 0.157 |

| С   | 1.35        | 1.75     | 0.053 | 0.069 |

| D   | 0.33        | 0.51     | 0.013 | 0.020 |

| G   | 1.27        | 1.27 BSC |       | 0 BSC |

| Н   | 0.10        | 0.25     | 0.004 | 0.010 |

| J   | 0.19        | 0.25     | 0.007 | 0.010 |

| K   | 0.40        | 1.27     | 0.016 | 0.050 |

| М   | 0 °         | 8 °      | 0 °   | 8 °   |

| N   | 0.25        | 0.50     | 0.010 | 0.020 |

| S   | 5.80        | 6.20     | 0.228 | 0.244 |

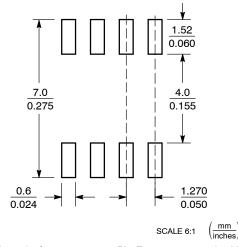

#### **SOLDERING FOOTPRINT\***

0.25 (0.010) M Z Y S

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the onsemi Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code = Assembly Location = Wafer Lot

= Year = Work Week W = Pb-Free Package

XXXXXX XXXXXX AYWW AYWW H  $\mathbb{H}$ Discrete **Discrete** (Pb-Free)

XXXXXX = Specific Device Code = Assembly Location Α

ww = Work Week

= Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

#### **STYLES ON PAGE 2**

| DOCUMENT NUMBER: | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Repository<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                                                                    | PAGE 1 OF 2 |  |

onsemi and ONSEMI. are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

#### SOIC-8 NB CASE 751-07 ISSUE AK

STYLE 3:

STYLE 2:

#### **DATE 16 FEB 2011**

STYLE 4:

| STYLE 1: PIN 1. EMITTER 2. COLLECTOR 3. COLLECTOR 4. EMITTER 5. EMITTER 6. BASE 7. BASE                                                                            | STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 3. COLLECTOR, #2 4. COLLECTOR, #2 5. BASE, #2 6. EMITTER, #2 7. BASE, #1                              | STYLE 3: PIN 1. DRAIN, DIE #1 2. DRAIN, #1 3. DRAIN, #2 4. DRAIN, #2 5. GATE, #2 6. SOURCE, #2 7. GATE, #1 8. SOURCE, #1                            | STYLE 4: PIN 1. ANODE 2. ANODE 3. ANODE 4. ANODE 5. ANODE 6. ANODE 7. ANODE                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8. EMITTER  STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN 4. DRAIN 5. GATE 6. GATE 7. SOURCE 8. SOURCE                                                                   | 8. EMITTER, #1  STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN 4. SOURCE 5. SOURCE 6. GATE 7. GATE 8. SOURCE                                                    | STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS 3. THIRD STAGE SOURCE 4. GROUND 5. DRAIN 6. GATE 3 7. SECOND STAGE Vd 8. FIRST STAGE Vd                    | 8. COMMON CATHODE  STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 3. BASE, #2 4. COLLECTOR, #2 5. COLLECTOR, #2 6. EMITTER, #2 7. EMITTER, #1 8. COLLECTOR, #1           |

| STYLE 9: PIN 1. EMITTER, COMMON 2. COLLECTOR, DIE #1 3. COLLECTOR, DIE #2 4. EMITTER, COMMON 5. EMITTER, COMMON 6. BASE, DIE #2 7. BASE, DIE #1 8. EMITTER, COMMON | STYLE 10: PIN 1. GROUND 2. BIAS 1 3. OUTPUT 4. GROUND 5. GROUND 6. BIAS 2 7. INPUT 8. GROUND                                                              | STYLE 11: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. DRAIN 2 7. DRAIN 1 8. DRAIN 1                                               | STYLE 12: PIN 1. SOURCE 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                                 |

| STYLE 13: PIN 1. N.C. 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                              | STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3. P-SOURCE 4. P-GATE 5. P-DRAIN 6. P-DRAIN 7. N-DRAIN 8. N-DRAIN                                                     | STYLE 15: PIN 1. ANODE 1 2. ANODE 1 3. ANODE 1 4. ANODE 1 5. CATHODE, COMMON 6. CATHODE, COMMON 7. CATHODE, COMMON 8. CATHODE, COMMON               | STYLE 16: PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 3. EMITTER, DIE #2 4. BASE, DIE #2 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 7. COLLECTOR, DIE #1 8. COLLECTOR, DIE #1 |

| STYLE 17: PIN 1. VCC 2. V2OUT 3. V1OUT 4. TXE 5. RXE 6. VEE 7. GND 8. ACC                                                                                          | STYLE 18: PIN 1. ANODE 2. ANODE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. CATHODE 8. CATHODE                                                                 | STYLE 19: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 8. MIRROR 1                                             | STYLE 20: PIN 1. SOURCE (N) 2. GATE (N) 3. SOURCE (P) 4. GATE (P) 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                   |

| STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3. CATHODE 3 4. CATHODE 4 5. CATHODE 5 6. COMMON ANODE 7. COMMON ANODE 8. CATHODE 6                                        | STYLE 22: PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3. COMMON CATHODE/VCC 4. I/O LINE 3 5. COMMON ANODE/GND 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND | STYLE 23: PIN 1. LINE 1 IN 2. COMMON ANODE/GND 3. COMMON ANODE/GND 4. LINE 2 IN 5. LINE 2 OUT 6. COMMON ANODE/GND 7. COMMON ANODE/GND 8. LINE 1 OUT | STYLE 24: PIN 1. BASE 2. EMITTER 3. COLLECTOR/ANODE 4. COLLECTOR/ANODE 5. CATHODE 6. CATHODE 7. COLLECTOR/ANODE 8. COLLECTOR/ANODE                                      |

| STYLE 25: PIN 1. VIN 2. N/C 3. REXT 4. GND 5. IOUT 6. IOUT 7. IOUT 8. IOUT                                                                                         | STYLE 26: PIN 1. GND 2. dv/dt 3. ENABLE 4. ILIMIT 5. SOURCE 6. SOURCE 7. SOURCE 8. VCC                                                                    | STYLE 27: PIN 1. ILIMIT 2. OVLO 3. UVLO 4. INPUT+ 5. SOURCE 6. SOURCE 7. SOURCE 8. DRAIN                                                            | STYLE 28: PIN 1. SW_TO_GND 2. DASIC_OFF 3. DASIC_SW_DET 4. GND 5. V MON 6. VBULK 7. VBULK 8. VIN                                                                        |

| STYLE 29: PIN 1. BASE, DIE #1 2. EMITTER, #1 3. BASE, #2 4. EMITTER, #2 5. COLLECTOR, #2 6. COLLECTOR, #2 7. COLLECTOR, #1 8. COLLECTOR, #1                        | STYLE 30: PIN 1. DRAIN 1 2. DRAIN 1 3. GATE 2 4. SOURCE 2 5. SOURCE 1/DRAIN 2 6. SOURCE 1/DRAIN 2 7. SOURCE 1/DRAIN 2 8. GATE 1                           |                                                                                                                                                     |                                                                                                                                                                         |

| DOCUMENT NUMBER: | 98ASB42564B | Printed versions are uncontrolled except when accessed directly from the Document Repositor<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                                                                | PAGE 2 OF 2 |  |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

STYLE 1:

onsemi, ONSEMI., and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems. or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales