Sample &

Buy

#### LMH6551

SNOSAK7D-FEBRUARY 2005-REVISED JANUARY 2015

## LMH6551 Differential, High-Speed Op Amp

Technical

Documents

### 1 Features

- 370 MHz -3-dB Bandwidth (V<sub>OUT</sub> = 0.5 V<sub>PP</sub>)

- 50 MHz 0.1-dB Bandwidth

- 2400 V/µs Slew Rate

- 18 ns Settling Time to 0.05%

- -94/-96 dB HD2/HD3 at 5 MHz

## 2 Applications

- Differential AD Driver

- Video Over Twisted-Pair

- Differential Line Driver

- Single End to Differential Converter

- High-Speed Differential Signaling

- IF/RF Amplifier

- SAW Filter Buffer/Driver

## 3 Description

Tools &

Software

The LMH6551 device is a high-performance voltage feedback differential amplifier and is part of the LMH<sup>™</sup> integrated circuits family of devices. The LMH6551 has the high speed and low distortion necessary for driving high-performance ADCs as well as the current handling capability to drive signals over balanced transmission lines like CAT 5 data cables. The LMH6551 can handle a wide range of video and data formats.

Support &

Community

20

With external gain set resistors, the LMH6551 can be used at any desired gain. Gain flexibility coupled with high speed makes the LMH6551 suitable for use as an IF amplifier in high-performance communications equipment.

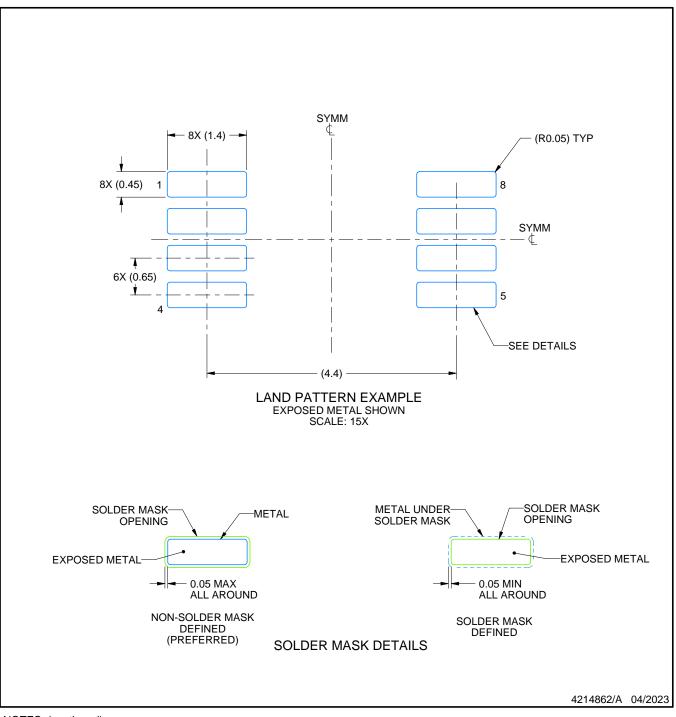

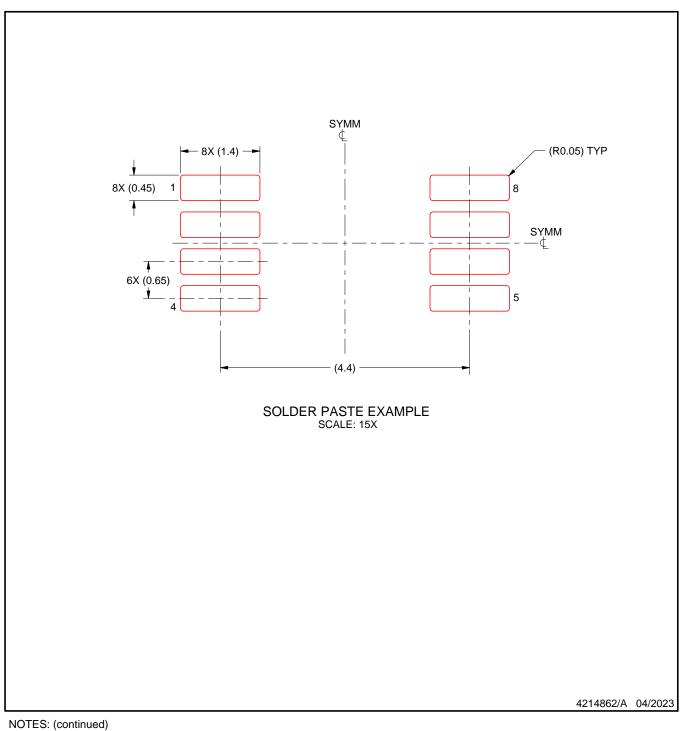

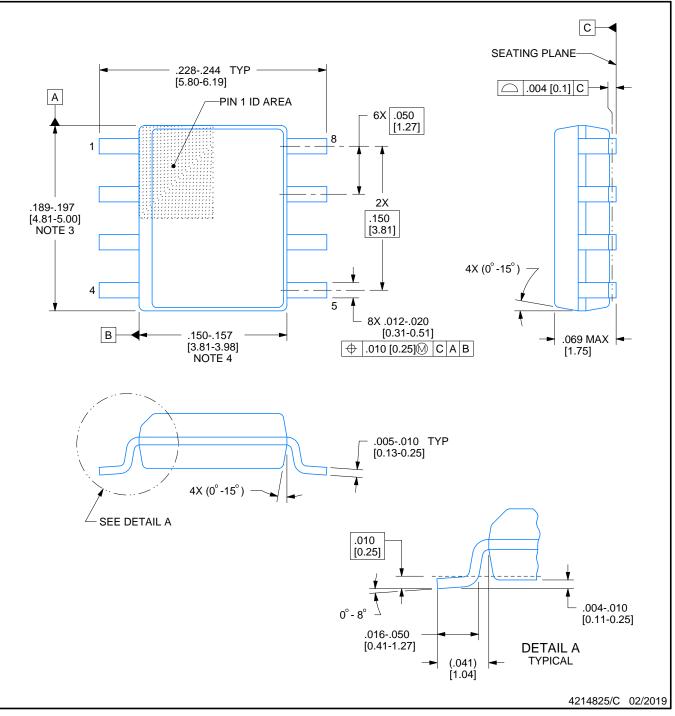

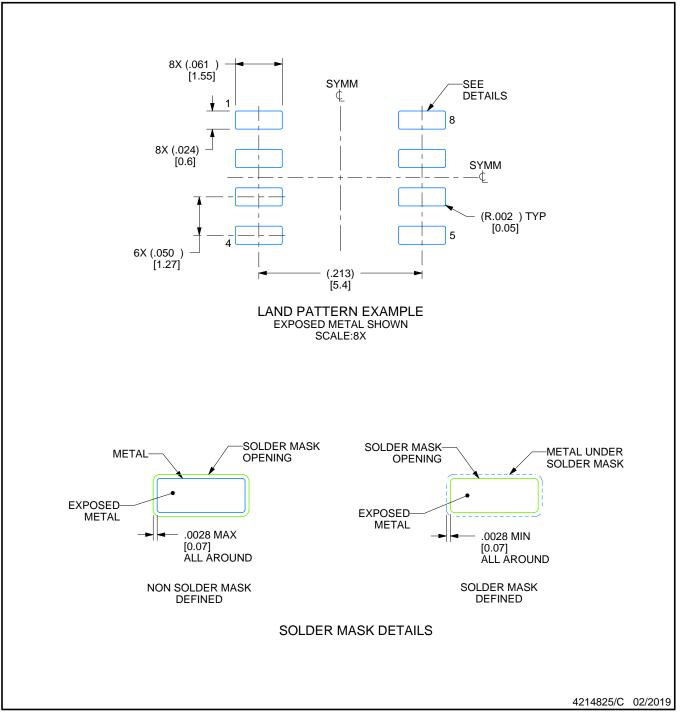

The LMH6551 is available in the space-saving SOIC and VSSOP packages.

#### Device Information<sup>(1)</sup>

| Device information |           |                   |  |  |  |  |

|--------------------|-----------|-------------------|--|--|--|--|

| PART NUMBER        | PACKAGE   | BODY SIZE (NOM)   |  |  |  |  |

| LMH6551            | SOIC (8)  | 4.90 mm × 3.91 mm |  |  |  |  |

|                    | VSSOP (8) | 3.00 mm × 3.00 mm |  |  |  |  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

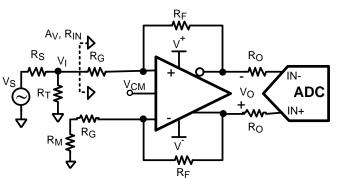

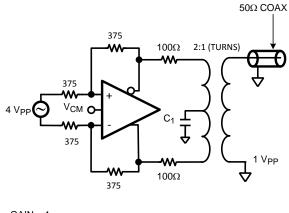

## 4 Typical Application

DesignTarget:

$$A_{v} = \frac{V_{O}}{V_{I}} \cong \frac{R_{F}}{R_{G}} \qquad 1) \text{ Set } R_{T} = \frac{1}{\frac{1}{R_{S}} - \frac{1}{R_{IN}}}$$

$$R_{IN} \cong \frac{2R_{G}(1+A_{v})}{2+A_{v}} \qquad 2) \text{ Set } R_{M} = R_{T} ||R_{S}|$$

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

## **Table of Contents**

| 1 | Feat | tures 1                                            |

|---|------|----------------------------------------------------|

| 2 | Арр  | lications 1                                        |

| 3 | Des  | cription1                                          |

| 4 | Тур  | ical Application 1                                 |

| 5 | Rev  | ision History 2                                    |

| 6 | Pin  | Configuration and Functions 3                      |

| 7 | Spe  | cifications 3                                      |

|   | 7.1  | Absolute Maximum Ratings 3                         |

|   | 7.2  | ESD Ratings 3                                      |

|   | 7.3  | Recommended Operating Conditions 4                 |

|   | 7.4  | Thermal Information 4                              |

|   | 7.5  | Electrical Characteristics: ±5 V 4                 |

|   | 7.6  | Electrical Characteristics: 5 V <sup>(4)</sup> 6   |

|   | 7.7  | Electrical Characteristics: 3.3 V <sup>(4)</sup> 7 |

|   | 7.8  | Typical Performance Characteristics                |

| 8 | Deta | ailed Description 13                               |

|   | 8.1  | Overview 13                                        |

|   | 8.2  | Functional Block Diagram 13                        |

|   |      |                                                    |

|    | 8.3  | Feature Description                      | 13 |

|----|------|------------------------------------------|----|

|    | 8.4  | Device Functional Modes                  | 13 |

| 9  | App  | lication and Implementation              | 14 |

|    | 9.1  | Application Information                  | 14 |

|    | 9.2  | Typical Applications                     | 14 |

| 10 | Pow  | ver Supply Recommendations               | 21 |

| 11 | Lay  | out                                      | 22 |

|    | 11.1 | Layout Guidelines                        | 22 |

|    | 11.2 | Layout Example                           | 22 |

|    | 11.3 | Power Dissipation                        | 23 |

|    | 11.4 | ESD Protection                           | 23 |

| 12 | Dev  | ice and Documentation Support            | 24 |

|    | 12.1 | Documentation Support                    | 24 |

|    | 12.2 | Trademarks                               | 24 |

|    | 12.3 | Electrostatic Discharge Caution          | 24 |

|    | 12.4 | Glossary                                 | 24 |

| 13 |      | hanical, Packaging, and Orderable mation | 24 |

**5 Revision History** NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C | hanges from Revision C (March 2013) to Revision D                                                                                                                                                                                                                                   | Page |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section |      |

| C | hanges from Revision B (March 2013) to Revision C                                                                                                                                                                                                                                   | Page |

| • | Changed layout of National Data Sheet to TI format                                                                                                                                                                                                                                  | 22   |

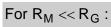

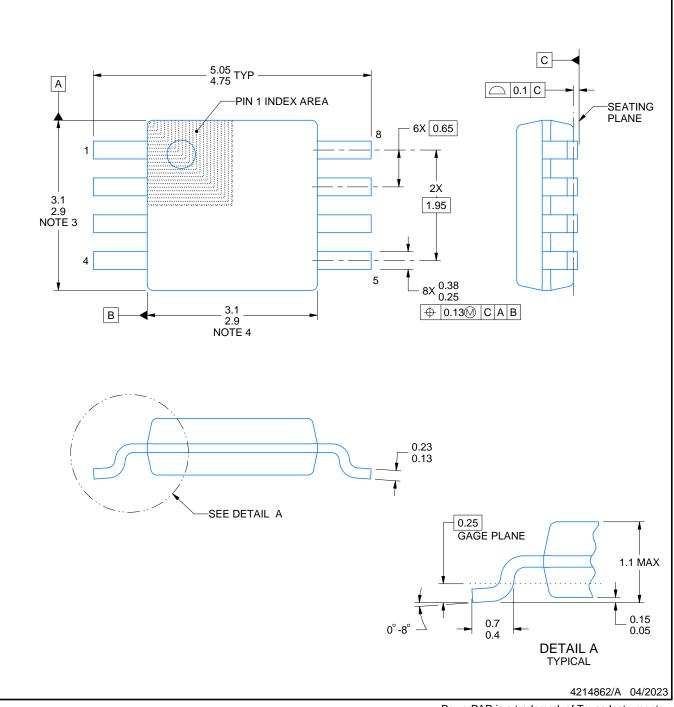

### 6 Pin Configuration and Functions

#### **Pin Functions**

|                                                                                         | PIN | I/O               | DESCRIPTION                |  |  |  |

|-----------------------------------------------------------------------------------------|-----|-------------------|----------------------------|--|--|--|

| NAME         NO.           -IN         1           VCM         2           V+         3 |     | 1/0               | DESCRIPTION                |  |  |  |

| -IN                                                                                     | 1   | I                 | Negative Input             |  |  |  |

| VCM 2 I                                                                                 |     | I                 | Output Common-Mode Voltage |  |  |  |

| V+                                                                                      | 3   | P Positive Supply |                            |  |  |  |

| +OUT                                                                                    | 4   | 0                 | Positive Output            |  |  |  |

| -OUT                                                                                    | 5   | 0                 | Negative Output            |  |  |  |

| V-                                                                                      | 6   | Р                 | Negative Supply            |  |  |  |

| NC                                                                                      | 7   | —                 | No Connection              |  |  |  |

| +IN                                                                                     | 8   | I                 | Positive Input             |  |  |  |

## 7 Specifications

## 7.1 Absolute Maximum Ratings (1)(2)(3)

|                                         | MIN | MAX              | UNIT |

|-----------------------------------------|-----|------------------|------|

| Supply Voltage                          |     | 13.2             | V    |

| Common-Mode Input Voltage               |     | ±Vs              | V    |

| Maximum Input Current (pins 1, 2, 7, 8) |     | 30               | mA   |

| Maximum Output Current (pins 4, 5)      | Se  | e <sup>(4)</sup> |      |

| Maximum Junction Temperature            |     | 150              | °C   |

| Storage Temperature, T <sub>stg</sub>   | -65 | 150              | °C   |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Recommended Operating Conditions indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications, see the Electrical Characteristics tables.

(2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

(3) For Soldering Information, see Product Folder at www.ti.com and SNOA549.

(4) The maximum output current (I<sub>OUT</sub>) is determined by device power dissipation limitations.

### 7.2 ESD Ratings

|                    |                         |                                                                   | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------|-------|------|

| V                  | Electrostatia discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Machine model (MM)                                                | ±200  | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

|                             | MIN | NOM MAX | UNIT |

|-----------------------------|-----|---------|------|

| Operating Temperature Range | -40 | +125    | °C   |

| Total Supply Voltage        | 3   | 12      | V    |

### 7.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup>                                          | LMH    |        |      |

|------------------------------------------------------------------------|--------|--------|------|

| THERMAL METRIC <sup>(1)</sup>                                          | D      | DGK    | UNIT |

|                                                                        | 8 PINS | 8 PINS |      |

| R <sub>0JA</sub> Junction-to-ambient thermal resistance <sup>(2)</sup> | 150    | 235    | °C/W |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

(2) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$  and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is P  $_{D}$ = ( $T_{J(MAX)} - T_A$ )/ $\theta_{JA}$ . All numbers apply for package soldered directly into a 2 layer PC board with zero air flow.

### 7.5 Electrical Characteristics: ±5 V<sup>(1)</sup>

Single-ended in differential out,  $T_A = 25^{\circ}$ C, G = +1,  $V_S = \pm 5$  V,  $V_{CM} = 0$  V,  $R_F = R_G = 365 \Omega$ ,  $R_L = 500 \Omega$ ; unless specified.

|                     | PARAMETER                                                        | TEST CON                                       | DITIONS                    | MIN <sup>(2)</sup> | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT   |

|---------------------|------------------------------------------------------------------|------------------------------------------------|----------------------------|--------------------|--------------------|--------------------|--------|

| AC PERF             | FORMANCE (DIFFERENTIAL)                                          |                                                |                            |                    |                    |                    |        |

| SSBW                | Small Signal -3 dB Bandwidth                                     | $V_{OUT} = 0.5 V_{PP}$                         |                            |                    | 370                |                    | MHz    |

| LSBW                | Large Signal −3 dB Bandwidth                                     | $V_{OUT} = 2 V_{PP}$                           |                            |                    | 340                |                    | MHz    |

|                     | Large Signal −3 dB Bandwidth                                     | $V_{OUT} = 4 V_{PP}$                           |                            |                    | 320                |                    | MHz    |

|                     | 0.1 dB Bandwidth                                                 | $V_{OUT} = 2 V_{PP}$                           |                            |                    | 50                 |                    | MHz    |

|                     | Slew Rate                                                        | 4-V Step <sup>(4)</sup>                        |                            |                    | 2400               |                    | V/µs   |

|                     | Rise/Fall Time                                                   | 2-V Step                                       |                            |                    | 1.8                |                    | ns     |

|                     | Settling Time                                                    | 2-V Step, 0.05%                                |                            |                    | 18                 |                    | ns     |

| V <sub>CM</sub> PIN | AC PERFORMANCE (COMMON-MOD                                       | E FEEDBACK AMPLIFIER                           | k)                         | ц                  |                    | 1                  |        |

|                     | Common-Mode Small Signal<br>Bandwidth                            | V <sub>CM</sub> bypass capacitor r             | emoved                     |                    | 200                |                    | MHz    |

| DISTOR              | TION AND NOISE RESPONSE                                          |                                                |                            |                    |                    |                    |        |

| HD2                 |                                                                  | V <sub>O</sub> = 2 V <sub>PP</sub> , f = 5 MHz | R <sub>L</sub> =800 Ω      |                    | -94                |                    | dBc    |

| HD2                 |                                                                  | V <sub>O</sub> = 2 V <sub>PP</sub> , f = 20MHz | , R <sub>L</sub> =800 Ω    |                    | -85                |                    | dBc    |

| HD3                 |                                                                  | $V_{O} = 2 V_{PP}$ , f = 5 MHz,                | R <sub>L</sub> =800 Ω      |                    | -96                |                    | dBc    |

| HD3                 |                                                                  | V <sub>O</sub> = 2 V <sub>PP</sub> , f = 20 MH | z, R <sub>L</sub> =800 Ω   |                    | -72                |                    | dBc    |

| en                  | Input Referred Voltage Noise                                     | Freq ≥ 1 MHz                                   |                            |                    | 6.0                |                    | nV/√Hz |

| i <sub>n</sub>      | Input Referred Noise Current                                     | Freq ≥ 1 MHz                                   |                            |                    | 1.5                |                    | pA/√Hz |

| INPUT C             | HARACTERISTICS (DIFFERENTIAL)                                    |                                                |                            |                    |                    |                    |        |

| V <sub>OSD</sub>    | Input Offset Voltage                                             | Differential Mode, VID                         |                            |                    | 0.5                | ±4                 | mV     |

|                     |                                                                  | $= 0, V_{CM} = 0$                              | At extreme<br>temperatures |                    |                    | ±6                 |        |

|                     | Input Offset Voltage Average<br>Temperature Drift <sup>(5)</sup> |                                                |                            |                    | -0.8               |                    | µV/°C  |

| I <sub>BI</sub>     | Input Bias Current <sup>(6)</sup>                                |                                                |                            |                    | -4                 | 0<br>-10           | μA     |

|                     | Input Bias Current Average<br>Temperature Drift <sup>(5)</sup>   |                                                |                            |                    | -2.6               |                    | nA/°C  |

(1) Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No specification of parametric performance is indicated in the electrical tables under conditions of internal self-heating where  $T_J > T_A$ .

(2) Limits are 100% production tested at 25°C. Limits over the operating temperature range are specified through correlation using Statistical Quality Control (SQC) methods.

(3) Typical numbers are the most likely parametric norm.

(4) Slew Rate is the average of the rising and falling edges.

(5) Drift determined by dividing the change in parameter at temperature extremes by the total temperature change.

(6) Negative input current implies current flowing out of the device.

4 Submit Documentation Feedback

## Electrical Characteristics: ±5 V<sup>(1)</sup> (continued)

|                        | PARAMETER                                                        | TEST CONDITIONS                                                                                                                                       |                              | MIN <sup>(2)</sup> | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT  |

|------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------|--------------------|--------------------|-------|

|                        | Input Bias Difference                                            | Difference in Bias curre<br>two inputs                                                                                                                | ents between the             |                    | 0.03               |                    | μA    |

| CMRR                   | Common-Mode Rejection Ratio                                      | DC, $V_{CM} = 0 V$ , $V_{ID} = 0$                                                                                                                     | V                            | 72                 | 80                 |                    | dBc   |

| R <sub>IN</sub>        | Input Resistance                                                 | Differential                                                                                                                                          |                              |                    | 5                  |                    | MΩ    |

| C <sub>IN</sub>        | Input Capacitance                                                | Differential                                                                                                                                          |                              |                    | 1                  |                    | pF    |

| CMVR                   | Input Common-Mode Voltage Range                                  | CMRR > 53dB                                                                                                                                           |                              | +3.1<br>-4.6       | +3.2<br>-4.7       |                    | V     |

| V <sub>CM</sub> PIN II | NPUT CHARACTERISTICS (COMMON-N                                   | ODE FEEDBACK AMP                                                                                                                                      | LIFIER)                      |                    |                    |                    |       |

| V <sub>OSC</sub>       | Input Offset Voltage                                             | Common Mode, $V_{ID}$ =                                                                                                                               |                              |                    | 0.5                | ±5                 | mV    |

|                        |                                                                  | 0                                                                                                                                                     | At extreme<br>temperatures   |                    |                    | ±8                 |       |

|                        | Input Offset Voltage Average<br>Temperature Drift <sup>(5)</sup> |                                                                                                                                                       |                              |                    | 8.2                |                    | µV/°C |

|                        | Input Bias Current <sup>(6)</sup>                                |                                                                                                                                                       |                              |                    | -2                 |                    | μA    |

|                        | V <sub>CM</sub> CMRR                                             | V <sub>ID</sub> = 0 V, 1-V step on<br>V <sub>OD</sub>                                                                                                 | V <sub>CM</sub> pin, measure | 70                 | 75                 |                    | dB    |

|                        | Input Resistance                                                 |                                                                                                                                                       |                              |                    | 25                 |                    | kΩ    |

|                        | Common-Mode Gain                                                 | $\Delta V_{O,CM} / \Delta V_{CM}$                                                                                                                     |                              | 0.995              | 0.999              | 1.005              | V/V   |

| OUTPUT                 | PERFORMANCE                                                      |                                                                                                                                                       |                              |                    |                    |                    |       |

|                        | Output Voltage Swing                                             | Single-Ended, Peak to                                                                                                                                 |                              | ±7.38              | ±7.8               |                    | V     |

|                        |                                                                  | Peak                                                                                                                                                  | At extreme<br>temperatures   | ±7.18              |                    |                    |       |

|                        | Output Common-Mode Voltage<br>Range                              | $V_{ID} = 0 V,$                                                                                                                                       |                              | ±3.69              | ±3.8               |                    | V     |

| I <sub>OUT</sub>       | Linear Output Current                                            | $V_{OUT} = 0V$                                                                                                                                        |                              | ±50                | ±65                |                    | mA    |

| I <sub>SC</sub>        | Short Circuit Current                                            | Output Shorted to Grou<br>V <sub>IN</sub> = 3-V Single-Ended                                                                                          |                              |                    | 140                |                    | mA    |

|                        | Output Balance Error                                             | $\begin{array}{l} \Delta V_{OUT}Common \ Mode \\ /\Delta V_{OUT} D {\it Ifferential} \ , \ V_O \\ D {\it ifferential} \ , \ f = 10 \ MHz \end{array}$ |                              |                    | -70                |                    | dB    |

| MISCELL                | ANEOUS PERFORMANCE                                               |                                                                                                                                                       |                              |                    |                    |                    |       |

| A <sub>VOL</sub>       | Open Loop Gain                                                   | Differential                                                                                                                                          |                              |                    | 70                 |                    | dB    |

| PSRR                   | Power Supply Rejection Ratio                                     | DC, $\Delta V_S = \pm 1 V$                                                                                                                            |                              | 74                 | 90                 |                    | dB    |

|                        | Supply Current                                                   | R <sub>L</sub> = ∞                                                                                                                                    |                              | 11                 | 12.5               | 14.5               | mA    |

|                        |                                                                  |                                                                                                                                                       | At extreme<br>temperatures   |                    |                    | 16.5               |       |

(7) The maximum output current ( $I_{OUT}$ ) is determined by device power dissipation limitations.

LMH6551

SNOSAK7D-FEBRUARY 2005-REVISED JANUARY 2015

www.ti.com

STRUMENTS

XAS

## 7.6 Electrical Characteristics: 5 V<sup>(1)</sup>

Single-ended in differential out, T<sub>A</sub>= 25°C, G = +1, V<sub>S</sub> = 5 V, V<sub>CM</sub> = 2.5 V, R<sub>F</sub> = R<sub>G</sub> = 365  $\Omega$ , R<sub>L</sub> = 500  $\Omega$ ; unless specified.

|                       | PARAMETER                                                        | TEST CONDI                                          | TIONS                                     | MIN <sup>(2)</sup> | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT               |

|-----------------------|------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------|--------------------|--------------------|--------------------|--------------------|

| SSBW                  | Small Signal −3 dB Bandwidth                                     | $R_L = 500 \ \Omega, \ V_{OUT} = 0.5$               | V <sub>PP</sub>                           |                    | 350                |                    | MHz                |

| LSBW                  | Large Signal −3 dB Bandwidth                                     | $R_L = 500 \ \Omega, \ V_{OUT} = 2 \ V$             | $R_L = 500 \Omega$ , $V_{OUT} = 2 V_{PP}$ |                    |                    |                    | MHz                |

|                       | 0.1 dB Bandwidth                                                 | $V_{OUT} = 2 V_{PP}$                                |                                           |                    | 50                 |                    | MHz                |

|                       | Slew Rate                                                        | 4-V Step <sup>(4)</sup>                             |                                           |                    | 1800               |                    | V/µs               |

|                       | Rise/Fall Time, 10% to 90%                                       | 4-V Step                                            |                                           |                    | 2                  |                    | ns                 |

|                       | Settling Time                                                    | 4-V Step, 0.05%                                     |                                           |                    | 17                 |                    | ns                 |

| V <sub>CM</sub> PIN   | AC PERFORMANCE (COMMON-MO                                        | DE FEEDBACK AMPLIFIEI                               | र)                                        |                    |                    |                    |                    |

|                       | Common-Mode Small Signal<br>Bandwidth                            |                                                     |                                           |                    | 170                |                    | MHz                |

| DISTOR                | TION AND NOISE RESPONSE                                          |                                                     |                                           |                    |                    |                    |                    |

| HD2                   | 2 <sup>nd</sup> Harmonic Distortion                              | V <sub>O</sub> = 2 V <sub>PP</sub> , f = 5 MHz, I   | R <sub>L</sub> =800 Ω                     |                    | -84                |                    | dBc                |

| HD2                   |                                                                  | V <sub>O</sub> = 2 V <sub>PP</sub> , f = 20 MHz,    | R <sub>L</sub> =800 Ω                     |                    | -69                |                    | dBc                |

| HD3                   | 3 <sup>rd</sup> Harmonic Distortion                              | V <sub>O</sub> = 2 V <sub>PP</sub> , f = 5 MHz, I   | R <sub>L</sub> =800 Ω                     |                    | -93                |                    | dBc                |

| HD3                   |                                                                  | V <sub>O</sub> = 2 V <sub>PP</sub> , f = 20 MHz,    | R <sub>L</sub> =800 Ω                     |                    | -67                |                    | dBc                |

| e <sub>n</sub>        | Input Referred Noise Voltage                                     | Freq ≥ 1 MHz                                        | Freq ≥ 1 MHz                              |                    | 6.0                |                    | nV/√Hz             |

| i <sub>n</sub>        | Input Referred Noise Current                                     | Freq ≥ 1 MHz                                        |                                           |                    | 1.5                |                    | pA/√ <del>Hz</del> |

| INPUT C               | HARACTERISTICS (DIFFERENTIAL                                     | )                                                   |                                           |                    |                    |                    |                    |

| V <sub>OSD</sub>      | Input Offset Voltage                                             | Differential Mode, V <sub>ID</sub> =                |                                           |                    | 0.5                | ±4                 | mV                 |

|                       |                                                                  | 0, $V_{CM} = 0$                                     | At extreme<br>temperatures                |                    |                    | ±6                 |                    |

|                       | Input Offset Voltage Average<br>Temperature Drift <sup>(5)</sup> |                                                     |                                           |                    | -0.8               |                    | µV/°C              |

| I <sub>BIAS</sub>     | Input Bias Current <sup>(6)</sup>                                |                                                     |                                           |                    | -4                 | 0<br>-10           | μA                 |

|                       | Input Bias Current Average<br>Temperature Drift <sup>(5)</sup>   |                                                     |                                           |                    | -3                 |                    | nA/°C              |

|                       | Input Bias Current Difference                                    | Difference in Bias currentwo inputs                 | nts between the                           |                    | 0.03               |                    | μA                 |

| CMRR                  | Common-Mode Rejection Ratio                                      | DC, $V_{ID} = 0 V$                                  |                                           | 70                 | 78                 |                    | dBc                |

|                       | Input Resistance                                                 | Differential                                        |                                           |                    | 5                  |                    | MΩ                 |

|                       | Input Capacitance                                                | Differential                                        |                                           |                    | 1                  |                    | pF                 |

| V <sub>ICM</sub>      | Input Common-Mode Range                                          | CMRR > 53 dB                                        |                                           | +3.1<br>+0.4       | +3.2<br>+0.3       |                    |                    |

| V <sub>CM</sub> PIN I | INPUT CHARACTERISTICS (COMMO                                     | ON-MODE FEEDBACK AM                                 | PLIFIER)                                  |                    |                    |                    |                    |

|                       | Input Offset Voltage                                             | Common Mode, V <sub>ID</sub> =                      |                                           |                    | 0.5                | ±5                 | mV                 |

|                       |                                                                  | 0 At e                                              | At extreme<br>temperatures                |                    |                    | ±8                 |                    |

|                       | Input Offset Voltage Average<br>Temperature Drift                |                                                     |                                           |                    | 5.8                |                    | μV/°C              |

|                       | Input Bias Current                                               |                                                     |                                           |                    | 3                  |                    | μA                 |

|                       | V <sub>CM</sub> CMRR                                             | $V_{ID} = 0,$<br>1V step on V <sub>CM</sub> pin, me | asure V <sub>OD</sub>                     | 70                 | 75                 |                    | dB                 |

|                       | Input Resistance                                                 | V <sub>CM</sub> pin to ground                       |                                           |                    | 25                 |                    | kΩ                 |

(1) Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that  $T_J = T_A$ . No specification of parametric performance is indicated in the electrical tables under conditions of internal self-heating where  $T_J > T_A$ .

(2) Limits are 100% production tested at 25°C. Limits over the operating temperature range are specified through correlation using Statistical Quality Control (SQC) methods.

(3) Typical numbers are the most likely parametric norm.

(4) Slew Rate is the average of the rising and falling edges.

(5) Drift determined by dividing the change in parameter at temperature extremes by the total temperature change.

(6) Negative input current implies current flowing out of the device.

6 Submit Documentation Feedback

## Electrical Characteristics: 5 V<sup>(1)</sup> (continued)

Single-ended in differential out,  $T_A$ = 25°C, G = +1,  $V_S$  = 5 V,  $V_{CM}$  = 2.5 V,  $R_F$  =  $R_G$  = 365  $\Omega$ ,  $R_L$  = 500  $\Omega$ ; unless specified.

|                  | PARAMETER                           | TEST CO                                                                                  | NDITIONS                      | MIN <sup>(2)</sup> | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT |

|------------------|-------------------------------------|------------------------------------------------------------------------------------------|-------------------------------|--------------------|--------------------|--------------------|------|

|                  | Common-Mode Gain                    | $\Delta V_{O,CM} / \Delta V_{CM}$                                                        |                               | 0.995              | 0.991              | 1.005              | V/V  |

| ουτρυτ           | <b>FPERFORMANCE</b>                 |                                                                                          |                               |                    |                    |                    |      |

| V <sub>OUT</sub> | Output Voltage Swing                | Single-Ended, Peak<br>V, V <sub>CM</sub> = 0 V                                           | k to Peak, $V_S$ = ±2.5       | ±2.4               | ±2.8               |                    | V    |

| I <sub>OUT</sub> | Linear Output Current               | V <sub>OUT</sub> = 0-V Differen                                                          | itial                         | ±45                | ±60                |                    | mA   |

| I <sub>SC</sub>  | Output Short Circuit Current        | Output Shorted to O<br>V <sub>IN</sub> = 3-V Single-En                                   | Ground<br>Ided <sup>(7)</sup> |                    | 230                |                    | mA   |

| CMVR             | Output Common-Mode Voltage<br>Range | $V_{ID} = 0, V_{CM}pin = 1$                                                              | .2 V and 3.8 V                | 3.72<br>1.23       | 3.8<br>1.2         |                    | V    |

|                  | Output Balance Error                | $\Delta V_{OUT}$ Common Mo<br>/ $\Delta V_{OUT}$ DIfferential,<br>Differential, f = 10 M | V <sub>OUT</sub> = 1Vpp       |                    | -65                |                    | dB   |

| MISCEL           | LANEOUS PERFORMANCE                 |                                                                                          |                               |                    |                    |                    |      |

|                  | Open Loop Gain                      | DC, Differential                                                                         |                               |                    | 70                 |                    | dB   |

| PSRR             | Power Supply Rejection Ratio        | DC, $\Delta V_S = \pm 0.5 V$                                                             | 72                            | 88                 |                    | dB                 |      |

| I <sub>S</sub>   | Supply Current                      | R <sub>L</sub> = ∞                                                                       |                               | 10                 | 11.5               | 13.5               | mA   |

|                  |                                     |                                                                                          | At extreme temperatures       |                    |                    | 15.5               |      |

(7) The maximum output current (I<sub>OUT</sub>) is determined by device power dissipation limitations.

## 7.7 Electrical Characteristics: 3.3 V<sup>(1)</sup>

Single-ended in differential out, T<sub>A</sub>= 25°C, G = +1, V<sub>S</sub> = 3.3 V, V<sub>CM</sub> = 1.65 V, R<sub>F</sub> = R<sub>G</sub> = 365  $\Omega$ , R<sub>L</sub> = 500  $\Omega$ ; unless specified.

|                     | PARAMETER                           | TEST CONDITIONS                                                 | MIN <sup>(2)</sup> TYP <sup>(3)</sup> MAX <sup>(2)</sup> | UNIT |

|---------------------|-------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------|------|

| SSBW                | Small Signal −3 dB Bandwidth        | $R_L = 500 \ \Omega$ , $V_{OUT} = 0.5 \ V_{PP}$                 | 320                                                      | MHz  |

| LSBW                | Large Signal −3 dB Bandwidth        | $R_L = 500 \ \Omega, \ V_{OUT} = 1 \ V_{PP}$                    | 300                                                      | MHz  |

|                     | Slew Rate                           | 1-V Step <sup>(4)</sup>                                         | 700                                                      | V/µs |

|                     | Rise/Fall Time, 10% to 90%          | 1-V Step                                                        | 2                                                        | ns   |

| V <sub>CM</sub> PIN | AC PERFORMANCE (COMMON-MOD          | E FEEDBACK AMPLIFIER)                                           |                                                          |      |

|                     | Common-Mode Small Signal Bandwidth  |                                                                 | 95                                                       | MHz  |

| DISTORT             | TION AND NOISE RESPONSE             |                                                                 |                                                          |      |

| HD2                 | 2 <sup>nd</sup> Harmonic Distortion | $V_O = 1 V_{PP}$ , f = 5 MHz, R <sub>L</sub> =800 $\Omega$      | -93                                                      | dBc  |

| HD2                 |                                     | $V_O = 1 V_{PP}$ , f = 20 MHz, R <sub>L</sub> =800 $\Omega$     | -74                                                      | dBc  |

| HD3                 | 3 <sup>rd</sup> Harmonic Distortion | $V_O = 1 V_{PP}$ , f = 5 MHz, R <sub>L</sub> =800 $\Omega$      | -85                                                      | dBc  |

| HD3                 |                                     | $V_{O}$ = 1 $V_{PP}$ , f = 20 MHz, R <sub>L</sub> =800 $\Omega$ | -69                                                      | dBc  |

(1) Electrical Table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device such that T<sub>J</sub> = T<sub>A</sub>. No specification of parametric performance is indicated in the electrical tables under conditions of internal self-heating where T<sub>J</sub> > T<sub>A</sub>.

(2) Limits are 100% production tested at 25°C. Limits over the operating temperature range are specified through correlation using Statistical Quality Control (SQC) methods.

(3) Typical numbers are the most likely parametric norm.

(4) Slew Rate is the average of the rising and falling edges.

## Electrical Characteristics: 3.3 V<sup>(1)</sup> (continued)

|--|

|                        | PARAMETER                                                        | TEST CONDITIONS                                                                                                                                                                  | MIN <sup>(2)</sup> TY | P <sup>(3)</sup> MAX | <sup>2)</sup> UNIT |

|------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|--------------------|

| INPUT CH               | HARACTERISTICS (DIFFERENTIAL)                                    |                                                                                                                                                                                  |                       |                      |                    |

| V <sub>OSD</sub>       | Input Offset Voltage                                             | Differential Mode, $V_{ID} = 0$ , $V_{CM} = 0$                                                                                                                                   |                       | 1                    | mV                 |

|                        | Input Offset Voltage Average<br>Temperature Drift <sup>(5)</sup> |                                                                                                                                                                                  |                       | 1.6                  | µV/°C              |

| I <sub>BIAS</sub>      | Input Bias Current <sup>(6)</sup>                                |                                                                                                                                                                                  |                       | -8                   | μA                 |

|                        | Input Bias Current Average<br>Temperature Drift <sup>(5)</sup>   |                                                                                                                                                                                  |                       | 9.5                  | nA/°C              |

|                        | Input Bias Current Difference                                    | Difference in Bias currents between the two inputs                                                                                                                               |                       | 0.3                  | μA                 |

| CMRR                   | Common-Mode Rejection Ratio                                      | DC, $V_{ID} = 0 V$                                                                                                                                                               |                       | 78                   | dBc                |

|                        | Input Resistance                                                 | Differential                                                                                                                                                                     |                       | 5                    | MΩ                 |

|                        | Input Capacitance                                                | Differential                                                                                                                                                                     |                       | 1                    | pF                 |

| V <sub>ICM</sub>       | Input Common-Mode Range                                          | CMRR > 53 dB                                                                                                                                                                     |                       | +1.5<br>+0.3         |                    |

| V <sub>CM</sub> PIN II | NPUT CHARACTERISTICS (COMMO                                      | N-MODE FEEDBACK AMPLIFIER)                                                                                                                                                       |                       |                      |                    |

|                        | Input Offset Voltage                                             | Common Mode, V <sub>ID</sub> = 0                                                                                                                                                 |                       | 1 :                  | 5 mV               |

|                        | Input Offset Voltage Average<br>Temperature Drift                |                                                                                                                                                                                  |                       | 18.6                 | µV/°C              |

|                        | Input Bias Current                                               |                                                                                                                                                                                  |                       | 3                    | μA                 |

|                        | V <sub>CM</sub> CMRR                                             | $V_{ID}$ = 0,<br>1-V step on $V_{CM}$ pin, measure $V_{OD}$                                                                                                                      |                       | 60                   | dB                 |

|                        | Input Resistance                                                 | $V_{CM}$ pin to ground                                                                                                                                                           |                       | 25                   | kΩ                 |

|                        | Common-Mode Gain                                                 | $\Delta V_{O,CM} / \Delta V_{CM}$                                                                                                                                                | 0                     | .999                 | V/V                |

| OUTPUT                 | PERFORMANCE                                                      |                                                                                                                                                                                  |                       |                      | ·                  |

| V <sub>OUT</sub>       | Output Voltage Swing                                             | Single-Ended, Peak to Peak, V_S= 3.3 V, V_{CM}= 1.65 V                                                                                                                           | ±0.75                 | ±0.9                 | V                  |

| I <sub>OUT</sub>       | Linear Output Current                                            | V <sub>OUT</sub> = 0-V Differential                                                                                                                                              | ±30                   | ±40                  | mA                 |

| I <sub>SC</sub>        | Output Short Circuit Current                                     | Output Shorted to Ground $V_{IN} = 2$ -V Single-Ended <sup>(7)</sup>                                                                                                             |                       | 200                  | mA                 |

| CMVR                   | Output Common-Mode Voltage<br>Range                              | $V_{\text{ID}}$ = 0, $V_{\text{CM}}\text{pin}$ = 1.2 V and 2.1 V                                                                                                                 |                       | 2.1<br>1.2           | V                  |

|                        | Output Balance Error                                             | $ \begin{array}{l} \Delta V_{OUT}Common \mbox{ Mode } /\Delta V_{OUT} D \mbox{ Ifferential,} \\ V_{OUT} = 1 \mbox{-} Vpp \mbox{ Differential, } f = 10 \mbox{ MHz} \end{array} $ |                       | -65                  | dB                 |

| MISCELL                | ANEOUS PERFORMANCE                                               | ·                                                                                                                                                                                |                       |                      |                    |

|                        | Open Loop Gain                                                   | DC, Differential                                                                                                                                                                 |                       | 70                   | dB                 |

| PSRR                   | Power Supply Rejection Ratio                                     | DC, $\Delta V_{S} = \pm 0.5 V$                                                                                                                                                   |                       | 75                   | dB                 |

| I <sub>S</sub>         | Supply Current                                                   | R <sub>L</sub> = ∞                                                                                                                                                               |                       | 8                    | mA                 |

(5) Drift determined by dividing the change in parameter at temperature extremes by the total temperature change.

(6) Negative input current implies current flowing out of the device.

(7) The maximum output current (I<sub>OUT</sub>) is determined by device power dissipation limitations.

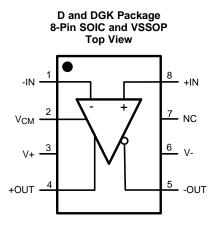

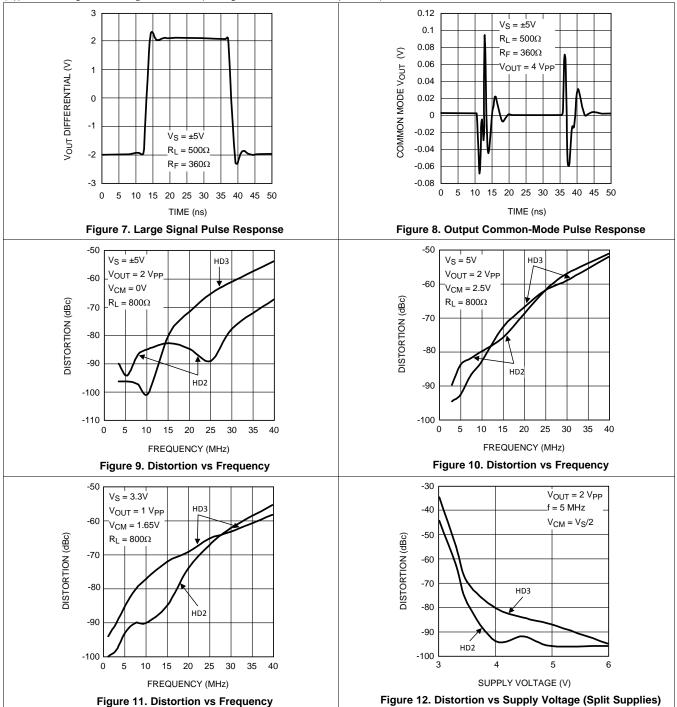

#### 7.8 Typical Performance Characteristics

(T<sub>A</sub> = 25°C, V<sub>S</sub> = ±5 V, R<sub>L</sub> = 500  $\Omega$ , R<sub>F</sub> = R<sub>G</sub> = 365  $\Omega$ ; Unless Specified).

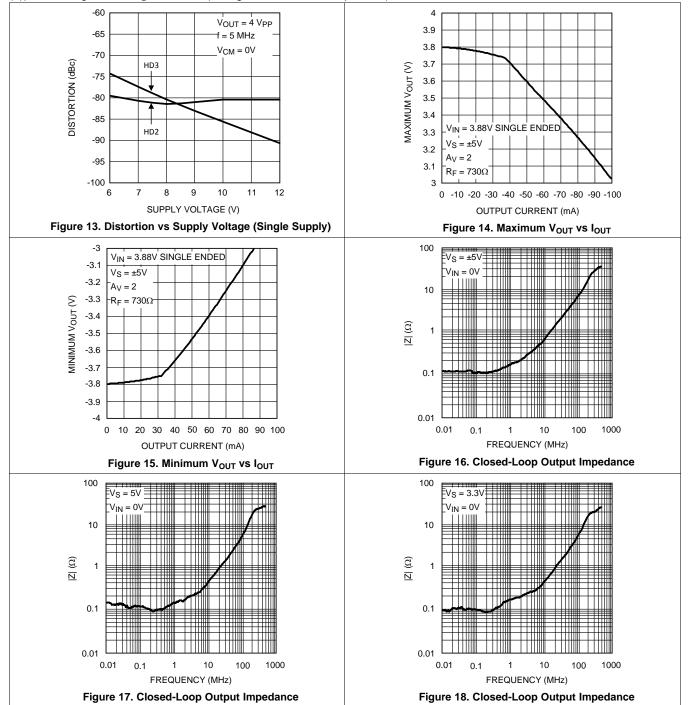

## **Typical Performance Characteristics (continued)**

$(T_A = 25^{\circ}C, V_S = \pm 5 V, R_L = 500 \Omega, R_F = R_G = 365 \Omega$ ; Unless Specified).

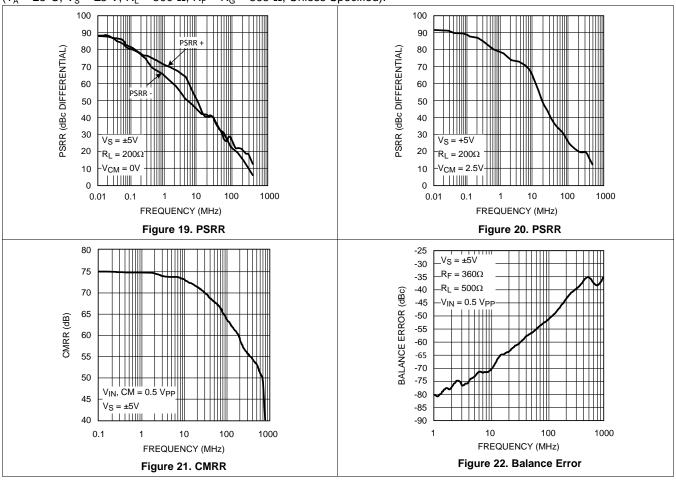

### **Typical Performance Characteristics (continued)**

$(T_A = 25^{\circ}C, V_S = \pm 5 V, R_L = 500 \Omega, R_F = R_G = 365 \Omega$ ; Unless Specified).

## **Typical Performance Characteristics (continued)**

$(T_A = 25^{\circ}C, V_S = \pm 5 V, R_L = 500 \Omega, R_F = R_G = 365 \Omega$ ; Unless Specified).

## 8 Detailed Description

#### 8.1 Overview

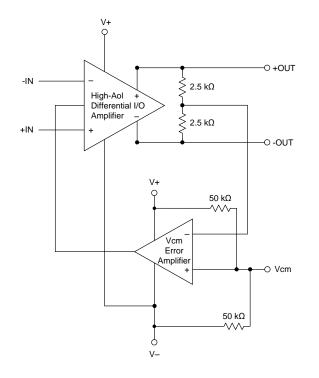

The LMH6551 is a fully differential amplifier designed to provide low distortion amplification to wide bandwidth differential signals. The LMH6551, though fully integrated for ultimate balance and distortion performance, functionally provides three channels. Two of these channels are the V+ and V- signal path channels, which function similarly to inverting mode operational amplifiers and are the primary signal paths. The third channel is the common-mode feedback circuit. This is the circuit that sets the output common mode as well as driving the V+ and V- outputs to be equal magnitude and opposite phase, even when only one of the two input channels is driven. The common-mode feedback circuit allows single-ended to differential operation.

### 8.2 Functional Block Diagram

#### 8.3 Feature Description

The LMH6551 combines a core differential I/O, high-gain block with an output common-mode sense that is compared to a reference voltage and then fed back into the main amplifier block to control the average output to that reference. The differential I/O block is a classic, high open-loop gain stage. The high-speed differential outputs include an internal averaging resistor network to sense the output common-mode voltage. This voltage is compared by a separate VCM error amplifier to the voltage on the VOCM pin. If floated, this reference is at half the total supply voltage across the device using two 50-k $\Omega$  resistors. This VCM error amplifier transmits a correction signal into the main amplifier to force the output average voltage to meet the target voltage on the VOCM pin.

### 8.4 Device Functional Modes

This wideband FDA requires external resistors for correct signal-path operation. When configured for the desired input impedance and gain setting with these external resistors, the amplifier can be either *on* with the PD pin asserted to a voltage greater than Vs- + 1.7 V, or turned *off* by asserting PD low. Disabling the amplifier shuts off the quiescent current and stops correct amplifier operation. The signal path is still present for the source signal through the external resistors. The VOCM control pin sets the output average voltage. Left open, VOCM defaults to an internal midsupply value. Driving this high-impedance input with a voltage reference within its valid range sets a target for the internal VCM error amplifier.

TEXAS INSTRUMENTS

www.ti.com

## 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 9.1 Application Information

The LMH6551 is a fully differential amplifier designed to provide low distortion amplification to wide bandwidth differential signals. The LMH6551, though fully integrated for ultimate balance and distortion performance, functionally provides three channels. Two of these channels are the V<sup>+</sup> and V<sup>-</sup> signal path channels, which function similarly to inverting mode operational amplifiers and are the primary signal paths. The third channel is the common-mode feedback circuit. This is the circuit that sets the output common mode as well as driving the V<sup>+</sup> and V<sup>-</sup> outputs to be equal magnitude and opposite phase, even when only one of the two input channels is driven. The common-mode feedback circuit allows single-ended to differential operation.

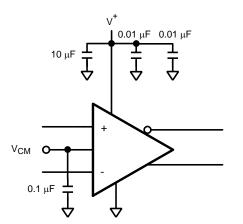

The LMH6551 is a voltage feedback amplifier with gain set by external resistors. Output common-mode voltage is set by the  $V_{CM}$  pin. This pin should be driven by a low impedance reference and should be bypassed to ground with a 0.1  $\mu$ F ceramic capacitor. Any signal coupling into the  $V_{CM}$  will be passed along to the output and will reduce the dynamic range of the amplifier.

#### 9.2 Typical Applications

#### 9.2.1 Typical Fully Differential Application

#### 9.2.1.1 Design Requirements

Applications using fully differential amplifiers have several requirements. The main requirements are high linearity and good signal amplitude. Linearity is accomplished by using well matched feedback and gain set resistors as well as an appropriate supply voltage. The signal amplitude can be tailored by using an appropriate gain. In this design, the gain is set for a gain of 2 (Rf=500/ RG=250) and the distortion criteria is better than -90 dBc at a frequency of 5 Mhz for HD2 and HD3. The supply voltage is set for  $\pm 5$  V and the output common mode is 0 V.

#### 9.2.1.2 Detailed Design Procedure

#### 9.2.1.2.1 Fully Differential Operation

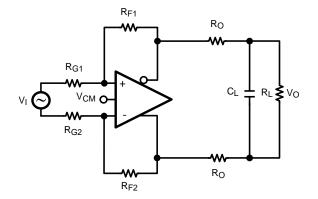

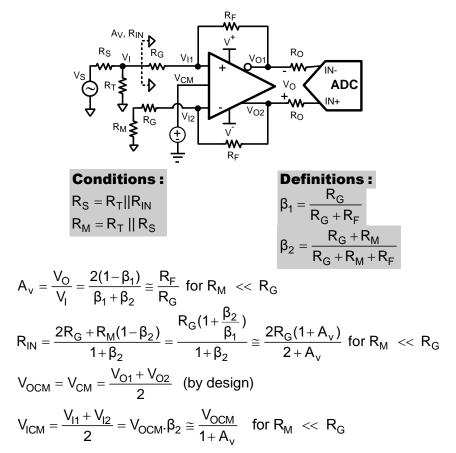

The LMH6551 will perform best when used with split supplies and in a fully differential configuration. See Figure 23 and Figure 24 for recommend circuits.

#### **Typical Applications (continued)**

The circuit shown in Figure 23 is a typical fully differential application as might be used to drive an ADC. In this circuit closed loop gain,  $(A_V) = V_{OUT}/V_{IN} = R_F/R_G$ . For all the applications in this data sheet  $V_{IN}$  is presumed to be the voltage presented to the circuit by the signal source. For differential signals this will be the difference of the signals on each input (which will be double the magnitude of each individual signal), while in single-ended inputs it will just be the driven input signal.

The resistors  $R_O$  help keep the amplifier stable when presented with a load  $C_L$  as is typical in an analog to digital converter (ADC). When fed with a differential signal, the LMH6551 provides excellent distortion, balance and common-mode rejection provided the resistors  $R_F$ ,  $R_G$  and  $R_O$  are well matched and strict symmetry is observed in board layout. With a DC CMRR of over 80dB, the DC and low frequency CMRR of most circuits will be dominated by the external resistors and board trace resistance. At higher frequencies board layout symmetry becomes a factor as well. Precision resistors of at least 0.1% accuracy are recommended and careful board layout will also be required.

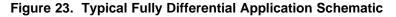

Figure 24. Fully Differential Cable Driver

With up to 15  $V_{PP}$  differential output voltage swing and 80 mA of linear drive current the LMH6551 makes an excellent cable driver as shown in Figure 24. The LMH6551 is also suitable for driving differential cables from a single-ended source.

The LMH6551 requires supply bypassing capacitors as shown in Figure 25 and Figure 26. The 0.01  $\mu$ F and 0.1  $\mu$ F capacitors should be leadless SMT ceramic capacitors and should be no more than 3 mm from the supply pins. The SMT capacitors should be connected directly to a ground plane. Thin traces or small vias will reduce the effectiveness of bypass capacitors. Also shown in both figures is a capacitor from the V<sub>CM</sub> pin to ground. The V<sub>CM</sub> pin is a high impedance input to a buffer which sets the output common-mode voltage. Any noise on this input is transferred directly to the output. Output common-mode noise will result in loss of dynamic range, degraded CMRR, degraded Balance and higher distortion. The V<sub>CM</sub> pin should be bypassed even if the pin in not used. There is an internal resistive divider on chip to set the output common-mode voltage to the mid point of the supply pins. The impedance looking into this pin is approximately 25 k $\Omega$ . If a different output common-mode voltage is desired drive this pin with a clean, accurate voltage reference.

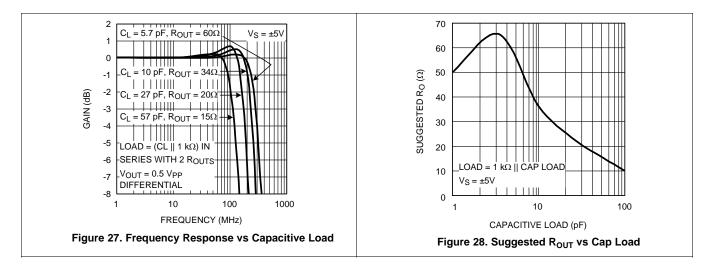

As noted in Driving Analog-to-Digital Converters, capacitive loads should be isolated from the amplifier output with small valued resistors. This is particularly the case when the load has a resistive component that is 500  $\Omega$  or higher. A typical ADC has capacitive components of around 10 pF and the resistive component could be 1000 Ω or higher. If driving a transmission line, such as  $50-\Omega$  coaxial or  $100-\Omega$  twisted pair, using matching resistors will be sufficient to isolate any subsequent capacitance. For other applications see Figure 28 and Figure 4 in Typical Performance Characteristics.

#### 9.2.1.3 Application Curves

Many application circuits will have capacitive loading. As shown in Figure 4, amplifier bandwidth is reduced with increasing capacitive load, so parasitic capacitance should be strictly limited.

In order to guarantee stability resistance should be added between the capacitive load and the amplifier output pins. The value of the resistor is dependent on the amount of capacitive load as shown in Figure 5. This resistive value is a suggestion. System testing will be required to determine the optimal value. Using a smaller resistor will retain more system bandwidth at the expense of overshoot and ringing, while larger values of resistance will reduce overshoot but will also reduce system bandwidth.

0.01 µF

0.01 μF

Figure 25. Split Supply Bypassing Capacitors

0.1 μF

Typical Applications (continued)

۷см

0.1 uF

9.2.1.2.2 Capacitive Drive

Figure 26. Single Supply Bypassing Capacitors

www.ti.com

#### **Typical Applications (continued)**

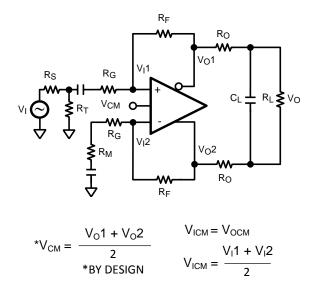

#### 9.2.2 Single-Ended Input to Differential Output

The LMH6551 provides excellent performance as an active balun transformer. Figure 29 shows a typical application where an LMH6551 is used to produce a differential signal from a single-ended source.

In single-ended input operation the output common-mode voltage is set by the  $V_{CM}$  pin as in fully differential mode. Also, in this mode the common-mode feedback circuit must recreate the signal that is not present on the unused differential input pin. Figure 22 is the measurement of the effectiveness of this process. The common-mode feedback circuit is responsible for ensuring balanced output with a single-ended input. Balance error is defined as the amount of input signal that couples into the output common mode. It is measured as the undesired output common-mode swing divided by the signal on the input. Balance error can be caused by either a channel to channel gain error, or phase error. Either condition will produce a common-mode shift. Figure 22 measures the balance error with a single-ended input as that is the most demanding mode of operation for the amplifier.

Supply and  $V_{CM}$  pin bypassing are also critical in this mode of operation. See the above section on *Fully Differential Operation* for bypassing recommendations and also see Figure 25 and Figure 26 for recommended supply bypassing configurations.

#### Texas Instruments

www.ti.com

#### **Typical Applications (continued)**

#### 9.2.3 Single Supply Operation

The input stage of the LMH6551 has a built in offset of 0.7 V towards the lower supply to accommodate single supply operation with single-ended inputs. As shown in Figure 29, the input common-mode voltage is less than the output common voltage. It is set by current flowing through the feedback network from the device output. The input common-mode range of 0.4 V to 3.2 V places constraints on gain settings. Possible solutions to this limitation include AC coupling the input signal, using split power supplies and limiting stage gain. AC coupling with single supply is shown in Figure 30.

In Figure 29 closed loop gain =  $V_O / V_I \cong R_F / R_G$ , where  $V_I = V_S / 2$ , as long as  $R_M \ll R_G$ . Note that in singleended to differential operation  $V_I$  is measured single-ended while  $V_O$  is measured differentially. This means that gain is really 1/2 or 6 dB less when measured on either of the output pins separately. Additionally, note that the input signal at  $R_T$  (labeled as  $V_I$ ) is 1/2 of  $V_S$  when  $R_T$  is chosen to match  $R_S$  to  $R_{IN}$ .

$V_{ICM}$  = Input common-mode voltage =  $(V_{11}+V_{12}) / 2$ .

Figure 30. AC-Coupled for Single Supply Operation

#### **Typical Applications (continued)**

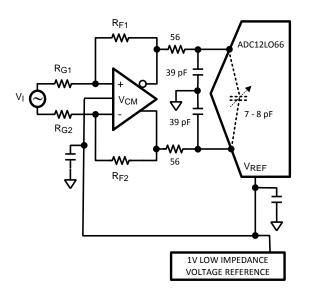

#### 9.2.4 Driving Analog-to-Digital Converters

Analog-to-digital converters (ADC) present challenging load conditions. They typically have high-impedance inputs with large and often variable capacitive components. As well, there are usually current spikes associated with switched capacitor or sample and hold circuits. Figure 31 shows a typical circuit for driving an ADC. The two 56- $\Omega$  resistors serve to isolate the capacitive loading of the ADC from the amplifier and ensure stability. In addition, the resistors form part of a low pass filter which helps to provide anti alias and noise reduction functions. The two 39-pF capacitors help to smooth the current spikes associated with the internal switching circuits of the ADC and also are a key component in the low pass filtering of the ADC input. In the circuit of Figure 31the cutoff frequency of the filter is  $1/(2^*\pi^*56 \Omega^*(39 \text{ pF} + 14\text{ pF})) = 53 \text{ MHz}$  (which is slightly less than the sampling frequency). Note that the ADC input capacitance must be factored into the frequency response of the input filter, and that being a differential input the effective input capacitance is double. Also as shown in Figure 31 the input capacitance to many ADCs is variable based on the clock cycle. See the data sheet for your particular ADC for details.

Figure 31. Driving an ADC

The amplifier and ADC should be located as closely together as possible. Both devices require that the filter components be in close proximity to them. The amplifier needs to have minimal parasitic loading on the output traces and the ADC is sensitive to high frequency noise that may couple in on its input lines. Some high performance ADCs have an input stage that has a bandwidth of several times its sample rate. The sampling process results in all input signals presented to the input stage mixing down into the Nyquist range (DC to Fs/2). See AN-236 for more details on the subsampling process and the requirements this imposes on the filtering necessary in your system.

#### **Typical Applications (continued)**

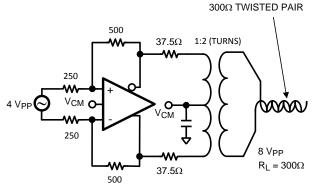

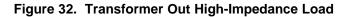

#### 9.2.5 Using Transformers

Transformers are useful for impedance transformation as well as for single to differential, and differential to single-ended conversion. A transformer can be used to step up the output voltage of the amplifier to drive very high impedance loads as shown in Figure 32. Figure 34 shows the opposite case where the output voltage is stepped down to drive a low-impedance load.

Transformers have limitations that must be considered before choosing to use one. Compared to a differential amplifier, the most serious limitations of a transformer are the inability to pass DC and balance error (which causes distortion and gain errors). For most applications the LMH6551 will have adequate output swing and drive current and a transformer will not be desirable. Transformers are used primarily to interface differential circuits to 50- $\Omega$  single-ended test equipment to simplify diagnostic testing.

$A_V = 2$

$$V_{L} = \frac{V_{IN} * A_{V} * N}{\left(\frac{2 R_{OUT} * N^{2}}{R_{L}} + 1\right)}$$

WHERE VIN = DIFFERENTIAL INPUT VOLTAGE

N = TRANSFORMER TURNS RATIO =

SECONDARY PRIMARY

$\label{eq:relation} \begin{array}{l} \mathsf{A}_{\mathsf{V}} = \mathsf{CLOSED} \ \mathsf{LOOP} \ \mathsf{AMPLIFIER} \ \mathsf{GAIN} \\ \mathsf{R}_{\mathsf{OUT}} = \ \mathsf{SERIES} \ \mathsf{OUTPUT} \ \mathsf{MATCHING} \ \mathsf{RESISTOR} \\ \mathsf{R}_{\mathsf{L}} = \mathsf{LOAD} \ \mathsf{RESISTOR} \end{array}$

$V_L = VOLTAGE ACROSS LOAD RESISTOR$

Figure 33. Calculating Transformer Circuit Net Gain

## **Typical Applications (continued)**

Figure 34. Transformer Out Low-Impedance Load

GAIN = 1C<sub>1</sub> IS NOT REQUIRED IF V<sub>CM</sub> = GROUND

#### Figure 35. Driving 50-Ω Test Equipment

### **10 Power Supply Recommendations**

The LMH6551 can be used with any combination of positive and negative power supplies as long as the combined supply voltage is between 4.5 V and 12 V. The LMH6551 will provide best performance when the output voltage is set at the mid supply voltage, and when the total supply voltage is between 9 V and 12 V. When selecting a supply voltage that is less than 9 V, it is important to consider both the input common-mode voltage range as well as the output voltage range.

Power supply bypassing as shown in Figure 25 and Figure 26 is important and power supply regulation should be within 5% or better when using a supply voltage near the edges of the operating range.

## 11 Layout

#### 11.1 Layout Guidelines

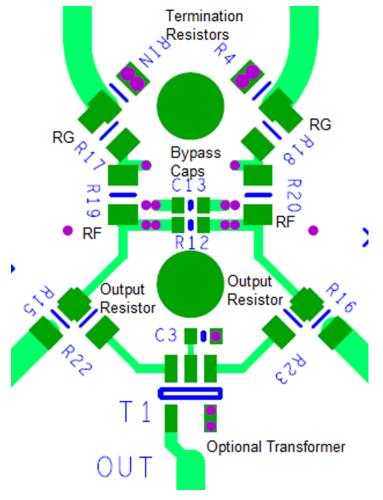

The LMH6551 is a very high performance amplifier. In order to get maximum benefit from the differential circuit architecture, board layout and component selection is very critical. The circuit board should have a low inductance ground plane and well bypassed broad supply lines. External components should be leadless surface mount types. The feedback network and output matching resistors should be composed of short traces and precision resistors (0.1%). The output matching resistors should be placed within 3-4 mm of the amplifier as should the supply bypass capacitors. The LMH730154 evaluation board is an example of good layout techniques.

The LMH6551 is sensitive to parasitic capacitances on the amplifier inputs and to a lesser extent on the outputs as well. Ground and power plane metal should be removed from beneath the amplifier and from beneath  $R_F$  and  $R_G$ .

With any differential signal path symmetry is very important. Even small amounts of asymmetry will contribute to distortion and balance errors.

Texas Instruments offers evaluation board(s) to aid in device testing and characterization and as a guide for proper layout. Generally, a good high frequency layout will keep power supply and ground traces away from the inverting input and output pins. Parasitic capacitances on these nodes to ground will cause frequency response peaking and possible circuit oscillations.

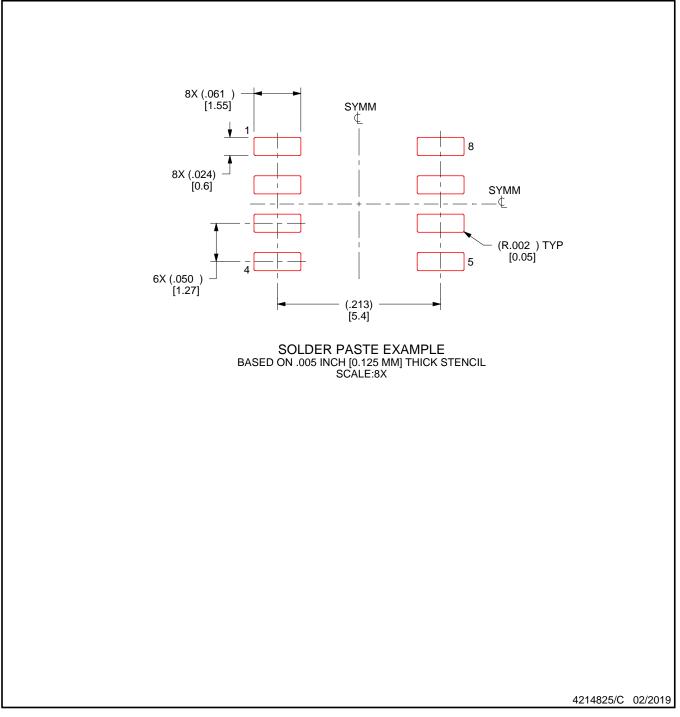

#### 11.2 Layout Example

Figure 36. Layout Schematic

#### 11.3 Power Dissipation

(1)

(3)

(4)

The LMH6551 is optimized for maximum speed and performance in the small form factor of the standard SOIC package, and is essentially a dual channel amplifier. To ensure maximum output drive and highest performance, thermal shutdown is not provided. Therefore, it is of utmost importance to make sure that the T<sub>JMAX</sub> of 150°C is never exceeded due to the overall power dissipation.

Follow these steps to determine the Maximum power dissipation for the LMH6551:

1. Calculate the quiescent (no-load) power:

$$\mathsf{P}_{\mathsf{AMP}} = \mathsf{I}_{\mathsf{CC}}^* (\mathsf{V}_{\mathsf{S}})$$

where

•

$$V_{S} = V^{+} - V^{-}$$

Be sure to include any current through the feedback network if  $V_{OCM}$  is not mid rail.

2. Calculate the RMS power dissipated in each of the output stages:

$$P_{D} (rms) = rms ((V_{S} - V_{OUT}^{+}) * I_{OUT}^{+}) + rms ((V_{S} - V_{OUT}^{-}) * I_{OUT}^{-})$$

where

V<sub>OUT</sub> and I<sub>OUT</sub> are the voltage and the current measured at the output pins of the differential amplifier as if they were single-ended amplifiers and V<sub>S</sub> is the total supply voltage

(2)

3. Calculate the total RMS power:

$$\mathsf{P}_{\mathsf{T}} = \mathsf{P}_{\mathsf{AMP}} + \mathsf{P}_{\mathsf{D}}.$$

The maximum power that the LMH6551 package can dissipate at a given temperature can be derived with the following equation:

$$\mathsf{P}_{\mathsf{MAX}} = (150^\circ - \mathsf{T}_{\mathsf{AMB}}) / \ \theta_{\mathsf{JA}}$$

where

- T<sub>AMB</sub> = Ambient temperature (°C)

- $\theta_{JA}$  = Thermal resistance, from junction to ambient, for a given package (°C/W)

- For the SOIC package  $\theta_{JA}$  is 150°C/W.

#### NOTE

If  $V_{CM}$  is not 0 V then there will be quiescent current flowing in the feedback network. This current should be included in the thermal calculations and added into the quiescent power dissipation of the amplifier.

### 11.4 ESD Protection