# Low Power, Low Noise Operational Amplifiers

# MC33178, MC33179

The MC33178/9 series is a family of high quality monolithic amplifiers employing Bipolar technology with innovative high performance concepts for quality audio and data signal processing applications. This device family incorporates the use of high frequency PNP input transistors to produce amplifiers exhibiting low input offset voltage, noise and distortion. In addition, the amplifier provides high output current drive capability while consuming only  $420\,\mu\text{A}$  of drain current per amplifier. The NPN output stage used, exhibits no deadband crossover distortion, large output voltage swing, excellent phase and gain margins, low open–loop high frequency output impedance, symmetrical source and sink AC frequency performance.

The MC33178/9 family offers both dual and quad amplifier versions in several package options.

#### **Features**

- 600 Ω Output Drive Capability

- Large Output Voltage Swing

- Low Offset Voltage: 0.15 mV (Mean)

- Low T.C. of Input Offset Voltage: 2.0 μV/°C

- Low Total Harmonic Distortion: 0.0024%

- (@ 1.0 kHz w/600  $\Omega$  Load)

- High Gain Bandwidth: 5.0 MHz

- High Slew Rate: 2.0 V/µs

- Dual Supply Operation: ±2.0 V to ±18 V

- ESD Clamps on the Inputs Increase Ruggedness without Affecting Device Performance

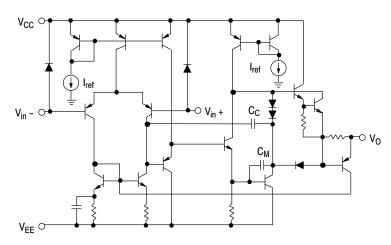

Figure 1. Representative Schematic Diagram (Each Amplifier)

**DUAL**

PDIP-8 P SUFFIX CASE 626

SOIC-8 D SUFFIX CASE 751

Micro8 DM SUFFIX CASE 846A

QUAD

PDIP-14 P SUFFIX CASE 646

SOIC-14 D SUFFIX CASE 751A

TSSOP-14 DTB SUFFIX CASE 948G

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 2 of this data sheet.

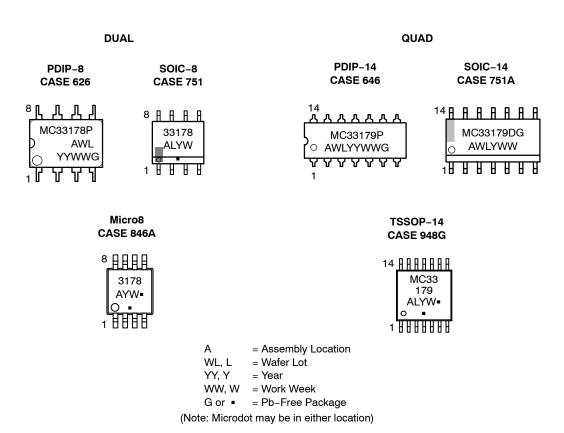

#### **DEVICE MARKING INFORMATION**

See general marking information in the device marking section on page 3 of this data sheet.

NOTE: Some of the devices on this data sheet have been **DISCONTINUED**. Please refer to the table on page 3.

#### **MAXIMUM RATINGS**

| Rating                                              | Symbol           | Value       | Unit |

|-----------------------------------------------------|------------------|-------------|------|

| Supply Voltage (V <sub>CC</sub> to V <sub>EE)</sub> | V <sub>S</sub>   | +36         | V    |

| Input Differential Voltage Range                    | $V_{IDR}$        | Note 1      | V    |

| Input Voltage Range                                 | $V_{IR}$         | Note 1      | V    |

| Output Short Circuit Duration (Note 2)              | t <sub>SC</sub>  | Indefinite  | sec  |

| Maximum Junction Temperature                        | TJ               | +150        | °C   |

| Storage Temperature Range                           | T <sub>stg</sub> | -60 to +150 | °C   |

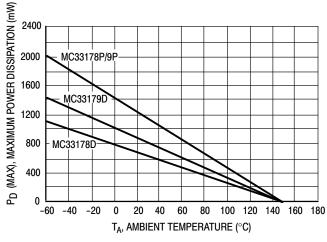

| Maximum Power Dissipation                           | $P_{D}$          | Note 2      | mW   |

| Operating Temperature Range                         | T <sub>A</sub>   | -40 to +85  | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. Either or both input voltages should not exceed  $V_{CC}$  or  $V_{EE}$ .

- Power dissipation must be considered to ensure maximum junction temperature (T<sub>J</sub>) is not exceeded. (See power dissipation performance characteristic, Figure 2.)

#### **ORDERING INFORMATION**

| Device        | Package               | Shipping <sup>†</sup> |

|---------------|-----------------------|-----------------------|

| MC33178DR2G   | SOIC-8<br>(Pb-Free)   | 2500 / Tape & Reel    |

| MC33178DMR2G  | Micro8<br>(Pb-Free)   | 4000 / Tape & Reel    |

| MC33179DR2G   | SOIC-14<br>(Pb-Free)  | 2500 / Tape & Reel    |

| MC33179DTBR2G | TSSOP-14<br>(Pb-Free) | 2500 / Tape & Reel    |

#### **DISCONTINUED** (Note 3)

| MC33178D    | SOIC-8               |                    |

|-------------|----------------------|--------------------|

| MC33178DG   | SOIC-8<br>(Pb-Free)  | 98 Units / Rail    |

| MC33178DR2  | SOIC-8               | 2500 / Tape & Reel |

| MC33178P    | PDIP-8               |                    |

| MC33178PG   | PDIP-8<br>(Pb-Free)  | 50 Units / Rail    |

| MC33178DMR2 | Micro8               | 4000 / Tape & Reel |

| MC33179D    | SOIC-14              |                    |

| MC33179DG   | SOIC-14<br>(Pb-Free) | 55 Units / Rail    |

| MC33179DR2  | SOIC-14              | 2500 / Tape & Reel |

| MC33179P    | PDIP-14              |                    |

| MC33179PG   | PDIP-14<br>(Pb-Free) | 25 Units / Rail    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

<sup>3.</sup> **DISCONTINUED:** These devices are not recommended for new design. Please contact your **onsemi** representative for information. The most current information on these devices may be available on <a href="https://www.onsemi.com">www.onsemi.com</a>.

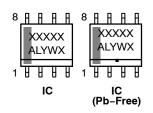

#### **MARKING DIAGRAMS**

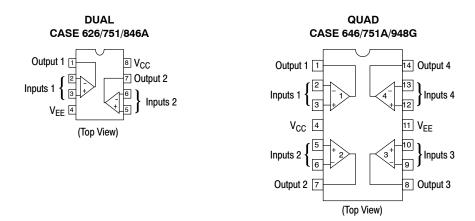

#### **PIN CONNECTIONS**

# **DC ELECTRICAL CHARACTERISTICS** ( $V_{CC}$ = +15 V, $V_{EE}$ = -15 V, $T_A$ = 25°C, unless otherwise noted.)

| Characteristics                                                                                                                                                                                                                                                                                                                                                      | Figure    | Symbol                                                                                                               | Min                              | Тур                                                       | Max                                    | Unit  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------------------------|----------------------------------------|-------|

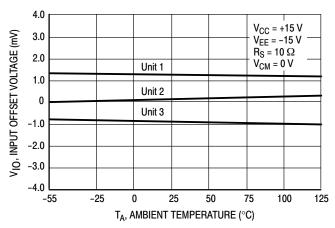

| Input Offset Voltage ( $R_S = 50 \ \Omega$ , $V_{CM} = 0 \ V$ , $V_O = 0 \ V$ ) ( $V_{CC} = +2.5 \ V$ , $V_{EE} = -2.5 \ V$ to $V_{CC} = +15 \ V$ , $V_{EE} = -15 \ V$ ) $T_A = +25^{\circ}C$ $T_A = -40^{\circ}$ to $+85^{\circ}C$                                                                                                                                  | 3         | V <sub>IO</sub>                                                                                                      | -<br>-                           | 0.15<br>-                                                 | 3.0<br>4.0                             | mV    |

| Average Temperature Coefficient of Input Offset Voltage<br>(R <sub>S</sub> = 50 $\Omega$ , V <sub>CM</sub> = 0 V, V <sub>O</sub> = 0 V)<br>T <sub>A</sub> = -40° to +85°C                                                                                                                                                                                            | 3         | $\Delta V_{IO}/\Delta T$                                                                                             | -                                | 2.0                                                       | -                                      | μV/°C |

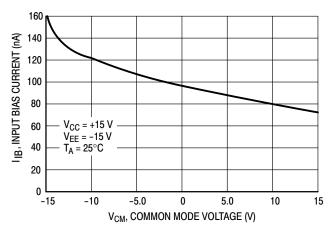

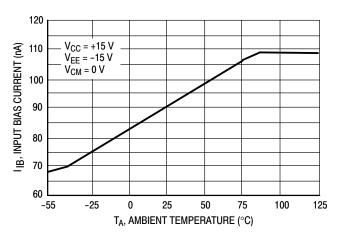

| Input Bias Current ( $V_{CM} = 0 \text{ V}, V_O = 0 \text{ V}$ ) $T_A = +25^{\circ}C$ $T_A = -40^{\circ} \text{ to } +85^{\circ}C$                                                                                                                                                                                                                                   | 4, 5      | I <sub>IB</sub>                                                                                                      | -<br>-                           | 100<br>-                                                  | 500<br>600                             | nA    |

| Input Offset Current ( $V_{CM} = 0 \text{ V}, V_O = 0 \text{ V}$ ) $T_A = +25^{\circ}C$ $T_A = -40^{\circ} \text{ to } +85^{\circ}C$                                                                                                                                                                                                                                 |           | lliol                                                                                                                | -<br>-                           | 5.0<br>–                                                  | 50<br>60                               | nA    |

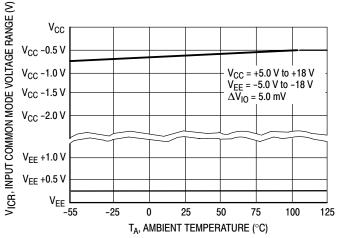

| Common Mode Input Voltage Range $(\Delta V_{IO} = 5.0 \text{ mV}, V_O = 0 \text{ V})$                                                                                                                                                                                                                                                                                | 6         | V <sub>ICR</sub>                                                                                                     | -13<br>-                         | -14<br>+14                                                | -<br>+13                               | V     |

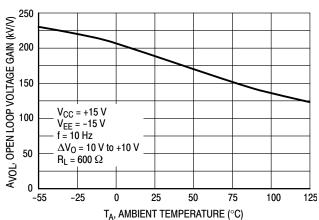

| Large Signal Voltage Gain ( $V_O$ = -10 V to +10 V, $R_L$ = 600 $\Omega$ ) $T_A$ = +25°C $T_A$ = -40° to +85°C                                                                                                                                                                                                                                                       | 7, 8      | A <sub>VOL</sub>                                                                                                     | 50<br>25                         | 200<br>–                                                  | -<br>-                                 | kV/V  |

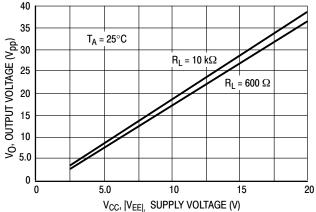

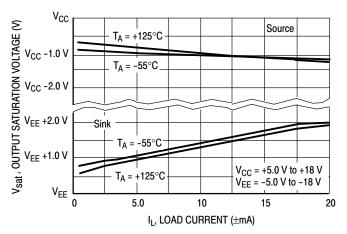

| Output Voltage Swing ( $V_{ID} = \pm 1.0 \text{ V}$ ) ( $V_{CC} = +15 \text{ V}$ , $V_{EE} = -15 \text{ V}$ ) $R_L = 300 \Omega$ $R_L = 300 \Omega$ $R_L = 600 \Omega$ $R_L = 600 \Omega$ $R_L = 600 \Omega$ $R_L = 2.0 \text{ k}\Omega$ $R_L = 2.0 \text{ k}\Omega$ ( $V_{CC} = +2.5 \text{ V}$ , $V_{EE} = -2.5 \text{ V}$ ) $R_L = 600 \Omega$ $R_L = 600 \Omega$ | 9, 10, 11 | V <sub>O</sub> +<br>V <sub>O</sub> -<br>V <sub>O</sub> +<br>V <sub>O</sub> -<br>V <sub>O</sub> +<br>V <sub>O</sub> - | -<br>+12<br>-<br>+13<br>-<br>1.1 | +12<br>-12<br>+13.6<br>-13<br>+14<br>-13.8<br>1.6<br>-1.6 | -<br>-<br>-12<br>-<br>-13<br>-<br>-1.1 | ٧     |

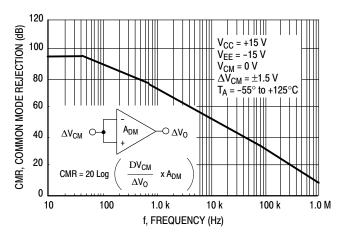

| Common Mode Rejection (V <sub>in</sub> = ±13 V)                                                                                                                                                                                                                                                                                                                      | 12        | CMR                                                                                                                  | 80                               | 110                                                       | -                                      | dB    |

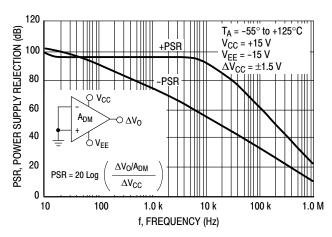

| Power Supply Rejection<br>V <sub>CC</sub> /V <sub>EE</sub> = +15 V/ -15 V, +5.0 V/ -15 V, +15 V/ -5.0 V                                                                                                                                                                                                                                                              | 13        | PSR                                                                                                                  | 80                               | 110                                                       | -                                      | dB    |

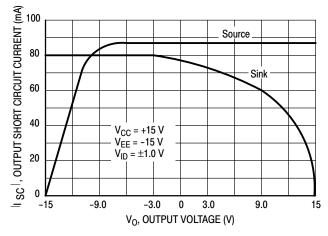

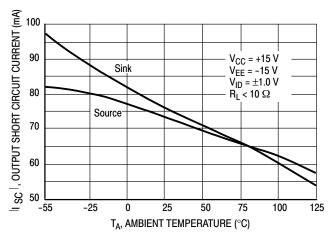

| Output Short Circuit Current ( $V_{ID}$ = $\pm 1.0$ V, Output to Ground)<br>Source ( $V_{CC}$ = 2.5 V to 15 V)<br>Sink ( $V_{EE}$ = -2.5 V to -15 V)                                                                                                                                                                                                                 | 14, 15    | I <sub>SC</sub>                                                                                                      | +50<br>-50                       | +80<br>-100                                               | <u> </u>                               | mA    |

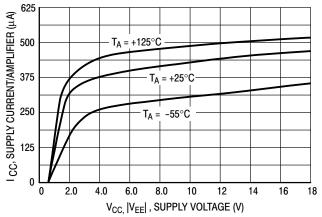

| Power Supply Current ( $V_O = 0 \text{ V}$ ) ( $V_{CC} = 2.5 \text{ V}$ , $V_{EE} = -2.5 \text{ V}$ to $V_{CC} = +15 \text{ V}$ , $V_{EE} = -15 \text{ V}$ ) MC33178 (Dual) $T_A = +25^{\circ}\text{C}$ $T_A = -40^{\circ} \text{ to } +85^{\circ}\text{C}$ MC33179 (Quad) $T_A = +25^{\circ}\text{C}$ $T_A = -40^{\circ} \text{ to } +85^{\circ}\text{C}$           | 16        | I <sub>D</sub>                                                                                                       | -<br>-<br>-                      | -<br>-<br>1.7<br>-                                        | 1.4<br>1.6<br>2.4<br>2.6               | mA    |

$\textbf{AC ELECTRICAL CHARACTERISTICS} \ (V_{CC} = +15 \ V, \ V_{EE} = -15 \ V, \ T_A = 25 ^{\circ}C, \ unless \ otherwise \ noted.)$

| Characteristics                                                                                                                                                     | Figure     | Symbol          | Min         | Тур                      | Max         | Unit   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------|-------------|--------------------------|-------------|--------|

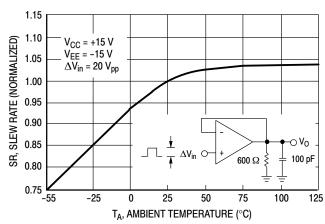

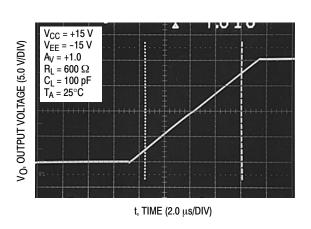

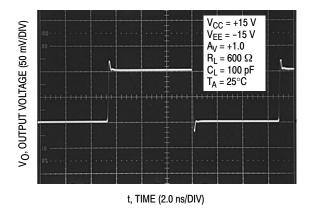

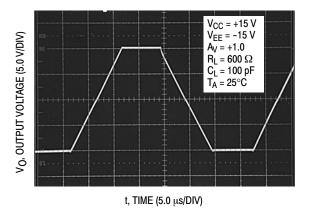

| Slew Rate $(V_{in}=-10~V~to~+10~V,~R_L=2.0~k\Omega,~C_L=100~pF,~A_V=+1.0~V)$                                                                                        | 17, 32     | SR              | 1.2         | 2.0                      | -           | V/μs   |

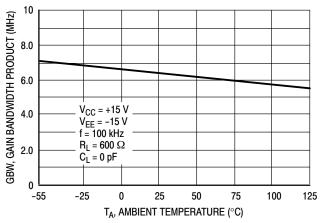

| Gain Bandwidth Product (f = 100 kHz)                                                                                                                                | 18         | GBW             | 2.5         | 5.0                      | -           | MHz    |

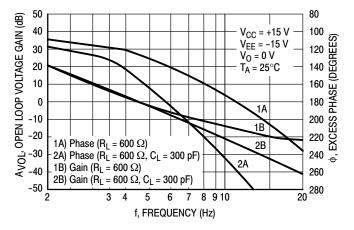

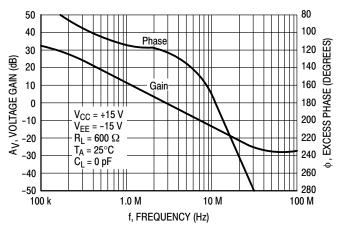

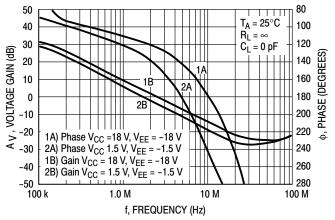

| AC Voltage Gain ( $R_L = 600 \Omega$ , $V_O = 0 V$ , $f = 20 kHz$ )                                                                                                 | 19, 20     | A <sub>VO</sub> | -           | 50                       | -           | dB     |

| Unity Gain Bandwidth (Open-Loop) (R <sub>L</sub> = 600 $\Omega$ , C <sub>L</sub> = 0 pF)                                                                            |            | BW              | -           | 3.0                      | -           | MHz    |

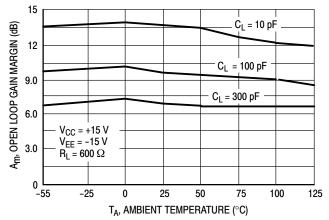

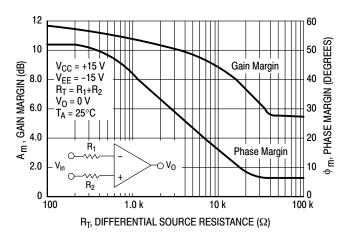

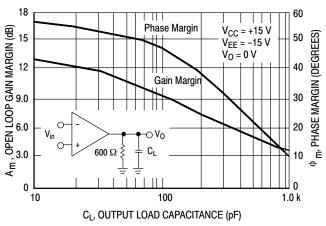

| Gain Margin ( $R_L = 600 \Omega$ , $C_L = 0 pF$ )                                                                                                                   | 21, 23, 24 | A <sub>m</sub>  | -           | 15                       | -           | dB     |

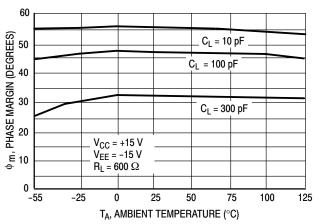

| Phase Margin ( $R_L = 600 \Omega$ , $C_L = 0 pF$ )                                                                                                                  | 22, 23, 24 | φm              | -           | 60                       | -           | Deg    |

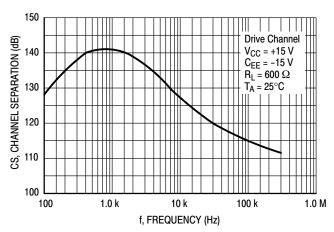

| Channel Separation (f = 100 Hz to 20 kHz)                                                                                                                           | 25         | CS              | -           | -120                     | -           | dB     |

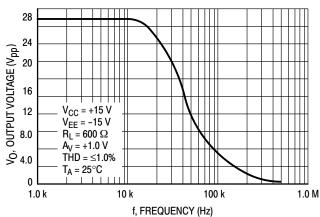

| Power Bandwidth ( $V_0$ = 20 $V_{pp}$ , $R_L$ = 600 $\Omega$ , THD $\leq$ 1.0%)                                                                                     |            | BW <sub>p</sub> | -           | 32                       | -           | kHz    |

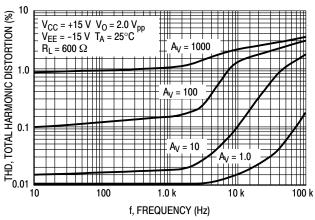

| Total Harmonic Distortion (R <sub>L</sub> = 600 $\Omega$ ,, V <sub>O</sub> = 2.0 V <sub>pp</sub> , A <sub>V</sub> = +1.0 V) (f = 1.0 kHz) (f = 10 kHz) (f = 20 kHz) | 26         | THD             | -<br>-<br>- | 0.0024<br>0.014<br>0.024 | -<br>-<br>- | %      |

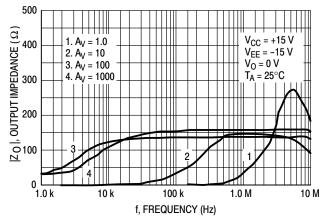

| Open Loop Output Impedance<br>(V <sub>O</sub> = 0 V, f = 3.0 MHz, A <sub>V</sub> = 10 V)                                                                            | 27         | Z <sub>O</sub>  | -           | 150                      | -           | Ω      |

| Differential Input Resistance (V <sub>CM</sub> = 0 V)                                                                                                               |            | R <sub>in</sub> | -           | 200                      | -           | kΩ     |

| Differential Input Capacitance (V <sub>CM</sub> = 0 V)                                                                                                              |            | C <sub>in</sub> | -           | 10                       | -           | pF     |

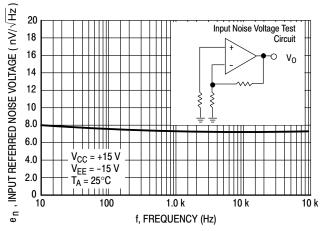

| Equivalent Input Noise Voltage (Rs = 100 $\Omega$ ,) f = 10 Hz f = 1.0 kHz                                                                                          | 28         | e <sub>n</sub>  | -<br>-      | 8.0<br>7.5               | -           | nV/√Hz |

| Equivalent Input Noise Current f = 10 Hz f = 1.0 kHz                                                                                                                | 29         | i <sub>n</sub>  | -<br>-      | 0.33<br>0.15             | 1 1         | pA/√Hz |

Figure 2. Maximum Power Dissipation versus Temperature

Figure 3. Input Offset Voltage versus Temperature for 3 Typical Units

Figure 4. Input Bias Current versus Common Mode Voltage

Figure 5. Input Bias Current versus Temperature

Figure 6. Input Common Mode Voltage Range versus Temperature

Figure 7. Open Loop Voltage Gain versus Temperature

Figure 8. Voltage Gain and Phase versus Frequency

Figure 9. Output Voltage Swing versus Supply Voltage

Figure 10. Output Saturation Voltage versus Load Current

Figure 11. Output Voltage versus Frequency

Figure 12. Common Mode Rejection versus Frequency Over Temperature

Figure 13. Power Supply Rejection versus Frequency Over Temperature

Figure 14. Output Short Circuit Current versus Output Voltage

Figure 15. Output Short Circuit Current versus Temperature

Figure 16. Supply Current versus Supply Voltage with No Load

Figure 17. Normalized Slew Rate versus Temperature

Figure 18. Gain Bandwidth Product versus Temperature

Figure 19. Voltage Gain and Phase versus Frequency

Figure 20. Voltage Gain and Phase versus Frequency

Figure 21. Open Loop Gain Margin versus Temperature

Figure 22. Phase Margin versus Temperature

Figure 23. Phase Margin and Gain Margin versus Differential Source Resistance

Figure 24. Open Loop Gain Margin and Phase Margin versus Output Load Capacitance

Figure 25. Channel Separation versus Frequency

Figure 26. Total Harmonic Distortion versus Frequency

Figure 27. Output Impedance versus Frequency

Figure 28. Input Referred Noise Voltage versus Frequency

Figure 29. Input Referred Noise Current versus Frequency

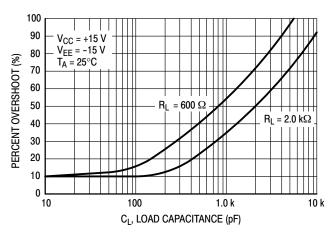

Figure 30. Percent Overshoot versus Load Capacitance

Figure 31. Non-inverting Amplifier Slew Rate

Figure 32. Small Signal Transient Response

Figure 33. Large Signal Transient Response

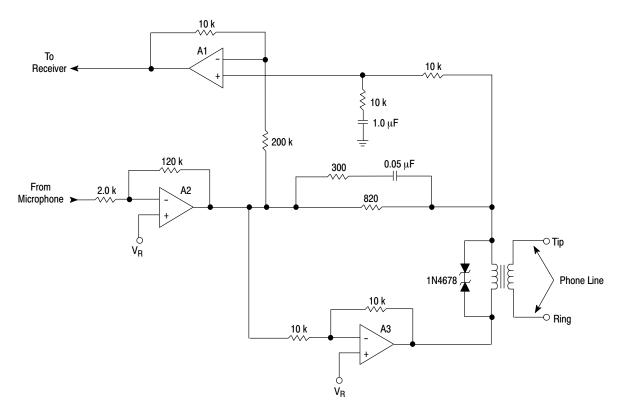

Figure 34. Telephone Line Interface Circuit

#### APPLICATION INFORMATION

This unique device uses a boosted output stage to combine a high output current with a drain current lower than similar bipolar input op amps. Its  $60^\circ$  phase margin and 15 dB gain margin ensure stability with up to 1000 pF of load capacitance (see Figure 24). The ability to drive a minimum 600  $\Omega$  load makes it particularly suitable for telecom applications. Note that in the sample circuit in Figure 34 both A2 and A3 are driving equivalent loads of approximately 600  $\Omega$  .

The low input offset voltage and moderately high slew rate and gain bandwidth product make it attractive for a variety of other applications. For example, although it is not single supply (the common mode input range does not include ground), it is specified at +5.0 V with a typical common mode rejection of 110 dB. This makes it an excellent choice for use with digital circuits. The high common mode rejection, which is stable over temperature, coupled with a low noise figure and low distortion, is an ideal op amp for audio circuits.

The output stage of the op amp is current limited and therefore has a certain amount of protection in the event of a short circuit. However, because of its high current output, it is especially important not to allow the device to exceed the maximum junction temperature, particularly with the MC33179 (quad op amp). Shorting more than one amplifier could easily exceed the junction temperature to the extent of causing permanent damage.

#### Stability

As usual with most high frequency amplifiers, proper lead dress, component placement, and PC board layout should be exercised for optimum frequency performance. For example, long unshielded input or output leads may result in unwanted input/output coupling. In order to preserve the relatively low input capacitance associated with these amplifiers, resistors connected to the inputs should be immediately adjacent to the input pin to minimize additional stray input capacitance. This not only minimizes the input pole frequency for optimum frequency response, but also minimizes extraneous "pick up" at this node. Supplying decoupling with adequate capacitance immediately adjacent to the supply pin is also important, particularly over temperature, since many types of decoupling capacitors exhibit great impedance changes over temperature.

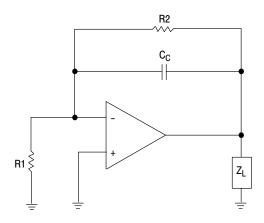

Additional stability problems can be caused by high load capacitances and/or a high source resistance. Simple compensation schemes can be used to alleviate these effects.

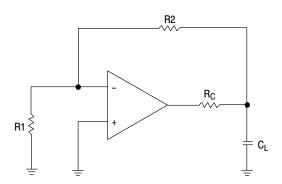

If a high source of resistance is used (R1 > 1.0 k $\Omega$ ), a compensation capacitor equal to or greater than the input capacitance of the op amp (10 pF) placed across the feedback resistor (see Figure 35) can be used to neutralize that pole and prevent outer loop oscillation. Since the closed loop transient response will be a function of that capacitance, it is important to choose the optimum value for that capacitor. This can be determined by the following Equation:

$$C_C = (1 + [R1/R2])^2 \times C_L (Z_O/R_2)$$

(1)

where: Z<sub>O</sub> is the output impedance of the op amp.

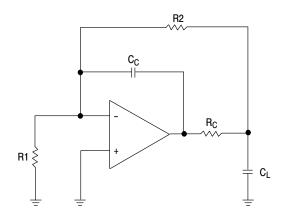

For moderately high capacitive loads (500 pF <  $C_L$  < 1500 pF) the addition of a compensation resistor on the order of  $20\,\Omega$  between the output and the feedback loop will help to decrease miller loop oscillation (see Figure 36). For high capacitive loads ( $C_L > 1500$  pF), a combined compensation scheme should be used (see Figure 37). Both the compensation resistor and the compensation capacitor affect the transient response and can be calculated for optimum performance. The value of  $C_C$  can be calculated using Equation 1. The Equation to calculate  $R_C$  is as follows:

$$R_C = Z_O \times R1/R2 \tag{2}$$

Figure 35. Compensation for High Source Impedance

Figure 36. Compensation Circuit for Moderate Capacitive Loads

Figure 37. Compensation Circuit for High Capacitive Loads

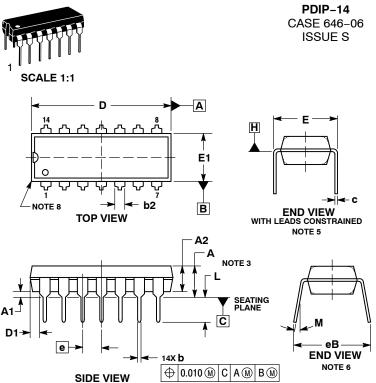

**DATE 22 APR 2015**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994. CONTROLLING DIMENSION: INCHES. DIMENSIONS A, A1 AND L ARE MEASURED WITH THE PACK-AGE SEATED IN JEDEC SEATING PLANE GAUGE GS-3. DIMENSIONS D, D1 AND E1 D0 NOT INCLUDE MOLD FLASH

- OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS ARE NOT TO EXCEED 0.10 INCH.

- DIMENSION E IS MEASURED AT A POINT 0.015 BELOW DATUM PLANE H WITH THE LEADS CONSTRAINED PERPENDICULAR TO DATUM C.

DIMENSION & B IS MEASURED AT THE LEAD TIPS WITH THE

- DIMENSION BY IS MEASURED AT THE LEAD TIFS WITH THE LEADS UNCONSTRAINED.

DATUM PLANE H IS COINCIDENT WITH THE BOTTOM OF THE LEADS, WHERE THE LEADS EXIT THE BODY.

PACKAGE CONTOUR IS OPTIONAL (ROUNDED OR SQUARE

|     | INCHES |       | MILLIM | ETERS |

|-----|--------|-------|--------|-------|

| DIM | MIN    | MAX   | MIN    | MAX   |

| Α   |        | 0.210 |        | 5.33  |

| A1  | 0.015  |       | 0.38   |       |

| A2  | 0.115  | 0.195 | 2.92   | 4.95  |

| b   | 0.014  | 0.022 | 0.35   | 0.56  |

| b2  | 0.060  | TYP   | 1.52   | TYP   |

| С   | 0.008  | 0.014 | 0.20   | 0.36  |

| D   | 0.735  | 0.775 | 18.67  | 19.69 |

| D1  | 0.005  |       | 0.13   |       |

| E   | 0.300  | 0.325 | 7.62   | 8.26  |

| E1  | 0.240  | 0.280 | 6.10   | 7.11  |

| е   | 0.100  | BSC   | 2.54   | BSC   |

| eB  |        | 0.430 |        | 10.92 |

| L   | 0.115  | 0.150 | 2.92   | 3.81  |

| M   |        | 10°   |        | 10°   |

#### **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code = Assembly Location

WL = Wafer Lot YY = Year WW = Work Week = Pb-Free Package G

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "■", may or may not be present. Some products may not follow the Generic Marking.

# **STYLES ON PAGE 2**

| DOCUMENT NUMBER: | 98ASB42428B | Electronic versions are uncontrolled except when accessed directly from<br>Printed versions are uncontrolled except when stamped "CONTROLLED" |             |

|------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | PDIP-14     |                                                                                                                                               | PAGE 1 OF 2 |

onsemi and Onsemi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries, onsemi reserves brisefin and of 160 m are trademarked so defined values of services and of the confined values and of the values of the confined values and of the values of the confined values and of the values of the special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

#### PDIP-14 CASE 646-06 ISSUE S

## **DATE 22 APR 2015**

| STYLE 1: PIN 1. COLLECTOR 2. BASE 3. EMITTER 4. NO CONNECTION 5. EMITTER 6. BASE 7. COLLECTOR 8. COLLECTOR 9. BASE 10. EMITTER 11. NO CONNECTION 12. EMITTER 13. BASE 14. COLLECTOR                                                                             | STYLE 2:<br>CANCELLED                                                                                                                                                                                                                                            | STYLE 3:<br>CANCELLED                                                                                                                                                                            | STYLE 4: PIN 1. DRAIN 2. SOURCE 3. GATE 4. NO CONNECTION 5. GATE 6. SOURCE 7. DRAIN 8. DRAIN 9. SOURCE 10. GATE 11. NO CONNECTION 12. GATE 13. SOURCE 14. DRAIN                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STYLE 5: PIN 1. GATE 2. DRAIN 3. SOURCE 4. NO CONNECTION 5. SOURCE 6. DRAIN 7. GATE 8. GATE 9. DRAIN 10. SOURCE 11. NO CONNECTION 12. SOURCE 13. DRAIN 14. GATE                                                                                                 | STYLE 6: PIN 1. COMMON CATHODE 2. ANODE/CATHODE 3. ANODE/CATHODE 4. NO CONNECTION 5. ANODE/CATHODE 6. NO CONNECTION 7. ANODE/CATHODE 8. ANODE/CATHODE 9. ANODE/CATHODE 10. NO CONNECTION 11. ANODE/CATHODE 12. ANODE/CATHODE 13. NO CONNECTION 14. COMMON ANODE  | STYLE 7: PIN 1. NO CONNECTION 2. ANODE 3. ANODE 4. NO CONNECTION 5. ANODE 6. NO CONNECTION 7. ANODE 8. ANODE 9. ANODE 10. NO CONNECTION 11. ANODE 12. ANODE 13. NO CONNECTION 14. COMMON CATHODE | STYLE 8: PIN 1. NO CONNECTION 2. CATHODE 3. CATHODE 4. NO CONNECTION 5. CATHODE 6. NO CONNECTION 7. CATHODE 8. CATHODE 9. CATHODE 10. NO CONNECTION 11. CATHODE 12. CATHODE 13. NO CONNECTION 14. COMMON ANODE                                                                     |

| STYLE 9: PIN 1. COMMON CATHODE 2. ANODE/CATHODE 3. ANODE/CATHODE 4. NO CONNECTION 5. ANODE/CATHODE 6. ANODE/CATHODE 7. COMMON ANODE 8. COMMON ANODE 9. ANODE/CATHODE 10. ANODE/CATHODE 11. NO CONNECTION 12. ANODE/CATHODE 13. ANODE/CATHODE 14. COMMON CATHODE | STYLE 10: PIN 1. COMMON CATHODE 2. ANODE/CATHODE 3. ANODE/CATHODE 4. ANODE/CATHODE 5. ANODE/CATHODE 6. NO CONNECTION 7. COMMON ANODE 8. COMMON CATHODE 9. ANODE/CATHODE 10. ANODE/CATHODE 11. ANODE/CATHODE 12. ANODE/CATHODE 13. NO CONNECTION 14. COMMON ANODE | STYLE 11: PIN 1. CATHODE 2. CATHODE 3. CATHODE 4. CATHODE 5. CATHODE 6. CATHODE 7. CATHODE 8. ANODE 9. ANODE 10. ANODE 11. ANODE 12. ANODE 13. ANODE 14. ANODE                                   | STYLE 12: PIN 1. COMMON CATHODE 2. COMMON ANODE 3. ANODE/CATHODE 4. ANODE/CATHODE 5. ANODE/CATHODE 6. COMMON ANODE 7. COMMON CATHODE 8. ANODE/CATHODE 9. ANODE/CATHODE 10. ANODE/CATHODE 11. ANODE/CATHODE 12. ANODE/CATHODE 13. ANODE/CATHODE 14. ANODE/CATHODE 14. ANODE/CATHODE |

| DOCUMENT NUMBER: | 98ASB42428B | Electronic versions are uncontrolled except when accessed directly from the Document Reposi<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | PDIP-14     |                                                                                                                                                                                | PAGE 2 OF 2 |

onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

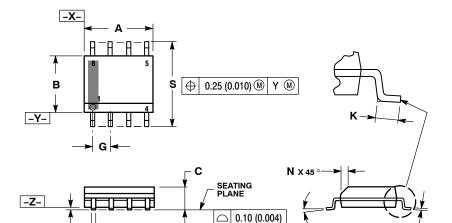

#### SOIC-8 NB CASE 751-07 **ISSUE AK**

**DATE 16 FEB 2011**

XS

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

|     | MILLIMETERS |       | INC       | HES   |

|-----|-------------|-------|-----------|-------|

| DIM | MIN         | MAX   | MIN       | MAX   |

| Α   | 4.80        | 5.00  | 0.189     | 0.197 |

| В   | 3.80        | 4.00  | 0.150     | 0.157 |

| С   | 1.35        | 1.75  | 0.053     | 0.069 |

| D   | 0.33        | 0.51  | 0.013     | 0.020 |

| G   | 1.27        | 7 BSC | 0.050 BSC |       |

| Н   | 0.10        | 0.25  | 0.004     | 0.010 |

| J   | 0.19        | 0.25  | 0.007     | 0.010 |

| K   | 0.40        | 1.27  | 0.016     | 0.050 |

| М   | 0 °         | 8 °   | 0 °       | 8 °   |

| N   | 0.25        | 0.50  | 0.010     | 0.020 |

| S   | 5.80        | 6.20  | 0.228     | 0.244 |

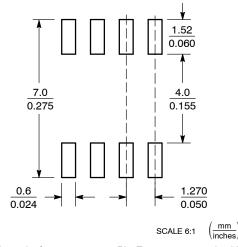

# **SOLDERING FOOTPRINT\***

0.25 (0.010) M Z Y S

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the onsemi Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code = Assembly Location = Wafer Lot

= Year = Work Week W = Pb-Free Package

XXXXXX XXXXXX AYWW AYWW H  $\mathbb{H}$ Discrete **Discrete** (Pb-Free)

XXXXXX = Specific Device Code = Assembly Location Α

ww = Work Week

= Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

#### **STYLES ON PAGE 2**

| DOCUMENT NUMBER: | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from Printed versions are uncontrolled except when stamped "CONTROLLED" |             |

|------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                            | PAGE 1 OF 2 |

onsemi and ONSEMI. are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

#### SOIC-8 NB CASE 751-07 ISSUE AK

STYLE 3:

STYLE 2:

#### **DATE 16 FEB 2011**

STYLE 4:

| STYLE 1: PIN 1. EMITTER 2. COLLECTOR 3. COLLECTOR 4. EMITTER 5. EMITTER 6. BASE 7. BASE                                                                            | STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 3. COLLECTOR, #2 4. COLLECTOR, #2 5. BASE, #2 6. EMITTER, #2 7. BASE, #1                              | STYLE 3: PIN 1. DRAIN, DIE #1 2. DRAIN, #1 3. DRAIN, #2 4. DRAIN, #2 5. GATE, #2 6. SOURCE, #2 7. GATE, #1 8. SOURCE, #1                            | STYLE 4: PIN 1. ANODE 2. ANODE 3. ANODE 4. ANODE 5. ANODE 6. ANODE 7. ANODE                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8. EMITTER  STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN 4. DRAIN 5. GATE 6. GATE 7. SOURCE 8. SOURCE                                                                   | 8. EMITTER, #1  STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN 4. SOURCE 5. SOURCE 6. GATE 7. GATE 8. SOURCE                                                    | STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS 3. THIRD STAGE SOURCE 4. GROUND 5. DRAIN 6. GATE 3 7. SECOND STAGE Vd 8. FIRST STAGE Vd                    | 8. COMMON CATHODE  STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 3. BASE, #2 4. COLLECTOR, #2 5. COLLECTOR, #2 6. EMITTER, #2 7. EMITTER, #1 8. COLLECTOR, #1           |

| STYLE 9: PIN 1. EMITTER, COMMON 2. COLLECTOR, DIE #1 3. COLLECTOR, DIE #2 4. EMITTER, COMMON 5. EMITTER, COMMON 6. BASE, DIE #2 7. BASE, DIE #1 8. EMITTER, COMMON | STYLE 10: PIN 1. GROUND 2. BIAS 1 3. OUTPUT 4. GROUND 5. GROUND 6. BIAS 2 7. INPUT 8. GROUND                                                              | STYLE 11: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. DRAIN 2 7. DRAIN 1 8. DRAIN 1                                               | STYLE 12: PIN 1. SOURCE 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                                 |

| STYLE 13: PIN 1. N.C. 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                              | STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3. P-SOURCE 4. P-GATE 5. P-DRAIN 6. P-DRAIN 7. N-DRAIN 8. N-DRAIN                                                     | STYLE 15: PIN 1. ANODE 1 2. ANODE 1 3. ANODE 1 4. ANODE 1 5. CATHODE, COMMON 6. CATHODE, COMMON 7. CATHODE, COMMON 8. CATHODE, COMMON               | STYLE 16: PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 3. EMITTER, DIE #2 4. BASE, DIE #2 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 7. COLLECTOR, DIE #1 8. COLLECTOR, DIE #1 |

| STYLE 17: PIN 1. VCC 2. V2OUT 3. V1OUT 4. TXE 5. RXE 6. VEE 7. GND 8. ACC                                                                                          | STYLE 18: PIN 1. ANODE 2. ANODE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. CATHODE 8. CATHODE                                                                 | STYLE 19: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 8. MIRROR 1                                             | STYLE 20: PIN 1. SOURCE (N) 2. GATE (N) 3. SOURCE (P) 4. GATE (P) 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                   |

| STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3. CATHODE 3 4. CATHODE 4 5. CATHODE 5 6. COMMON ANODE 7. COMMON ANODE 8. CATHODE 6                                        | STYLE 22: PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3. COMMON CATHODE/VCC 4. I/O LINE 3 5. COMMON ANODE/GND 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND | STYLE 23: PIN 1. LINE 1 IN 2. COMMON ANODE/GND 3. COMMON ANODE/GND 4. LINE 2 IN 5. LINE 2 OUT 6. COMMON ANODE/GND 7. COMMON ANODE/GND 8. LINE 1 OUT | STYLE 24: PIN 1. BASE 2. EMITTER 3. COLLECTOR/ANODE 4. COLLECTOR/ANODE 5. CATHODE 6. CATHODE 7. COLLECTOR/ANODE 8. COLLECTOR/ANODE                                      |

| STYLE 25: PIN 1. VIN 2. N/C 3. REXT 4. GND 5. IOUT 6. IOUT 7. IOUT 8. IOUT                                                                                         | STYLE 26: PIN 1. GND 2. dv/dt 3. ENABLE 4. ILIMIT 5. SOURCE 6. SOURCE 7. SOURCE 8. VCC                                                                    | STYLE 27: PIN 1. ILIMIT 2. OVLO 3. UVLO 4. INPUT+ 5. SOURCE 6. SOURCE 7. SOURCE 8. DRAIN                                                            | STYLE 28: PIN 1. SW_TO_GND 2. DASIC_OFF 3. DASIC_SW_DET 4. GND 5. V MON 6. VBULK 7. VBULK 8. VIN                                                                        |

| STYLE 29: PIN 1. BASE, DIE #1 2. EMITTER, #1 3. BASE, #2 4. EMITTER, #2 5. COLLECTOR, #2 6. COLLECTOR, #2 7. COLLECTOR, #1 8. COLLECTOR, #1                        | STYLE 30: PIN 1. DRAIN 1 2. DRAIN 1 3. GATE 2 4. SOURCE 2 5. SOURCE 1/DRAIN 2 6. SOURCE 1/DRAIN 2 7. SOURCE 1/DRAIN 2 8. GATE 1                           |                                                                                                                                                     |                                                                                                                                                                         |

| DOCUMENT NUMBER: | 98ASB42564B | Printed versions are uncontrolled except when accessed directly from the Docur<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in the Docur |             |  |

|------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                                                        | PAGE 2 OF 2 |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

STYLE 1:

△ 0.10

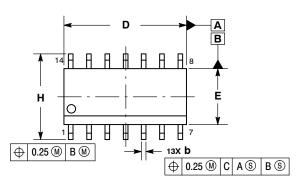

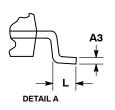

SOIC-14 NB CASE 751A-03 ISSUE L

**DATE 03 FEB 2016**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER

- ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

- DIMENSION b DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF AT

- MAXIMUM MATERIAL CONDITION.

DIMENSIONS D AND E DO NOT INCLUDE MOLD PROTRUSIONS.

- 5. MAXIMUM MOLD PROTRUSION 0.15 PER SIDE

|     | MILLIM   | IETERS | INC       | HES   |

|-----|----------|--------|-----------|-------|

| DIM | MIN      | MAX    | MIN       | MAX   |

| Α   | 1.35     | 1.75   | 0.054     | 0.068 |

| A1  | 0.10     | 0.25   | 0.004     | 0.010 |

| АЗ  | 0.19     | 0.25   | 0.008     | 0.010 |

| b   | 0.35     | 0.49   | 0.014     | 0.019 |

| D   | 8.55     | 8.75   | 0.337     | 0.344 |

| Е   | 3.80     | 4.00   | 0.150     | 0.157 |

| е   | 1.27 BSC |        | 0.050 BSC |       |

| Н   | 5.80     | 6.20   | 0.228     | 0.244 |

| h   | 0.25     | 0.50   | 0.010     | 0.019 |

| L   | 0.40     | 1.25   | 0.016     | 0.049 |

| M   | 0 °      | 7°     | 0 °       | 7°    |

#### **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code Α = Assembly Location

WL = Wafer Lot Υ = Year WW = Work Week = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "■", may or may not be present. Some products may not follow the Generic Marking.

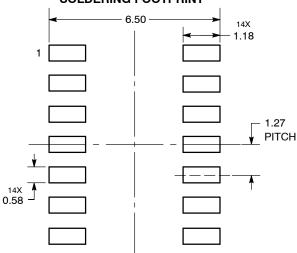

## **SOLDERING FOOTPRINT\***

DIMENSIONS: MILLIMETERS

C SEATING PLANE

#### **STYLES ON PAGE 2**

| DOCUMENT NUMBER: | 98ASB42565B | Electronic versions are uncontrolled except when accessed directly from<br>Printed versions are uncontrolled except when stamped "CONTROLLED" |             |

|------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | SOIC-14 NB  |                                                                                                                                               | PAGE 1 OF 2 |

onsemi and ONSEMI. are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the onsemi Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### SOIC-14 CASE 751A-03 ISSUE L

## DATE 03 FEB 2016

| STYLE 1: PIN 1. COMMON CATHODE 2. ANODE/CATHODE 3. ANODE/CATHODE 4. NO CONNECTION 5. ANODE/CATHODE 6. NO CONNECTION 7. ANODE/CATHODE 8. ANODE/CATHODE 9. ANODE/CATHODE 10. NO CONNECTION 11. ANODE/CATHODE 12. ANODE/CATHODE 13. NO CONNECTION 14. COMMON ANODE | STYLE 2:<br>CANCELLED                                                                                                                                         | STYLE 3: PIN 1. NO CONNECTION 2. ANODE 3. ANODE 4. NO CONNECTION 5. ANODE 6. NO CONNECTION 7. ANODE 8. ANODE 9. ANODE 10. NO CONNECTION 11. ANODE 12. ANODE 13. NO CONNECTION 14. COMMON CATHODE                                                                | STYLE 4: PIN 1. NO CONNECTION 2. CATHODE 3. CATHODE 4. NO CONNECTION 5. CATHODE 6. NO CONNECTION 7. CATHODE 8. CATHODE 9. CATHODE 10. NO CONNECTION 11. CATHODE 12. CATHODE 13. NO CONNECTION 14. COMMON ANODE                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STYLE 5: PIN 1. COMMON CATHODE 2. ANODE/CATHODE 3. ANODE/CATHODE 4. ANODE/CATHODE 5. ANODE/CATHODE 6. NO CONNECTION 7. COMMON ANODE 8. COMMON CATHODE 9. ANODE/CATHODE 10. ANODE/CATHODE 11. ANODE/CATHODE 12. ANODE/CATHODE 13. NO CONNECTION 14. COMMON ANODE | STYLE 6: PIN 1. CATHODE 2. CATHODE 3. CATHODE 4. CATHODE 5. CATHODE 6. CATHODE 7. CATHODE 8. ANODE 9. ANODE 10. ANODE 11. ANODE 12. ANODE 13. ANODE 14. ANODE | STYLE 7: PIN 1. ANODE/CATHODE 2. COMMON ANODE 3. COMMON CATHODE 4. ANODE/CATHODE 5. ANODE/CATHODE 6. ANODE/CATHODE 7. ANODE/CATHODE 8. ANODE/CATHODE 9. ANODE/CATHODE 10. ANODE/CATHODE 11. COMMON CATHODE 12. COMMON ANODE 13. ANODE/CATHODE 14. ANODE/CATHODE | STYLE 8: PIN 1. COMMON CATHODE 2. ANODE/CATHODE 3. ANODE/CATHODE 4. NO CONNECTION 5. ANODE/CATHODE 6. ANODE/CATHODE 7. COMMON ANODE 8. COMMON ANODE 9. ANODE/CATHODE 10. ANODE/CATHODE 11. NO CONNECTION 12. ANODE/CATHODE 13. ANODE/CATHODE 14. COMMON CATHODE |

| DOCUMENT NUMBER: | 98ASB42565B Electronic versions are uncontrolled except when accessed directly from th<br>Printed versions are uncontrolled except when stamped "CONTROLLED CO |  |             |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|

| DESCRIPTION:     | SOIC-14 NB                                                                                                                                                     |  | PAGE 2 OF 2 |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

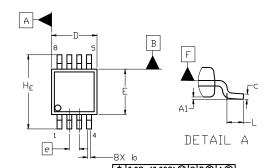

#### Micro8 CASE 846A-02 ISSUE K

**DATE 16 JUL 2020**

**♦** 0.08 (0.003)**₩** C BS AS NOTE 3 TOP VIEW

END VIEW

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 2009.

- CONTROLLING DIMENSION: MILLIMETERS

- DIMENSION 6 DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.10 mm IN EXCESS OF MAXIMUM MATERIAL CONDITION.

- DIMENSIONS D AND E DO NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.15 mm PER SIDE. DIMENSION E DDES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 mm PER SIDE. DIMENSIONS D AND E ARE DETERMINED AT DATUM F.

- DATUMS A AND B ARE TO BE DETERMINED AT DATUM F.

- A1 IS DEFINED AS THE VERTICAL DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT ON THE PACKAGE BODY.

MOUNTING FOOTPRINT

| DIM   | MI       | LLIMETE | RS   |

|-------|----------|---------|------|

| ואונע | MIN.     | N□M.    | MAX. |

| Α     |          |         | 1.10 |

| A1    | 0.05     | 0.08    | 0.15 |

| b     | 0.25     | 0.33    | 0.40 |

| c     | 0.13     | 0.18    | 0.23 |

| D     | 2.90     | 3.00    | 3.10 |

| Е     | 2.90     | 3.00    | 3.10 |

| е     | 0.65 BSC |         |      |

| HE    | 4.75     | 4.90    | 5.05 |

| L     | 0.40     | 0.55    | 0.70 |

#### **GENERIC MARKING DIAGRAM\***

XXXX = Specific Device Code Α = Assembly Location

Υ = Year W = Work Week = Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "■", may or may not be present. Some products may not follow the Generic Marking.

| STYLE 1:                 | STYLE 2:                   | STYLE 3:        |

|--------------------------|----------------------------|-----------------|

| PIN 1. SOURCE            | PIN 1. SOURCE 1            | PIN 1. N-SOURCE |

| <ol><li>SOURCE</li></ol> | 2. GATE 1                  | 2. N-GATE       |

| <ol><li>SOURCE</li></ol> | <ol><li>SOURCE 2</li></ol> | 3. P-SOURCE     |

| <ol><li>GATE</li></ol>   | 4. GATE 2                  | 4. P-GATE       |

| <ol><li>DRAIN</li></ol>  | 5. DRAIN 2                 | 5. P-DRAIN      |

| <ol><li>DRAIN</li></ol>  | 6. DRAIN 2                 | 6. P-DRAIN      |

| 7. DRAIN                 | 7. DRAIN 1                 | 7. N-DRAIN      |

| 8. Drain                 | 8. DRAIN 1                 | 8. N-DRAIN      |

| DOCUMENT NUMBER: | 98ASB14087C Electronic versions are uncontrolled except when accessed directly from the Printed versions are uncontrolled except when stamped "CONTROLLED CO |  |             |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|

| DESCRIPTION:     | MICRO8                                                                                                                                                       |  | PAGE 1 OF 1 |

onsemi and Onsemi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries, onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

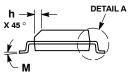

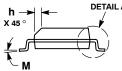

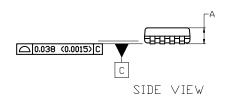

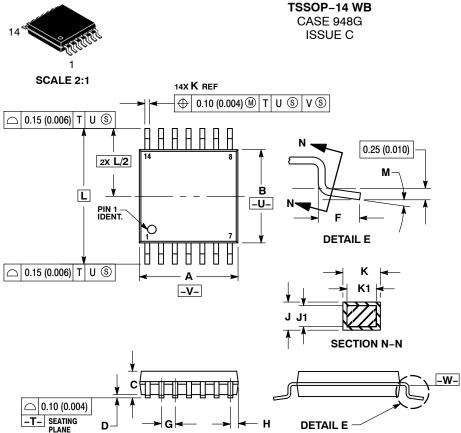

**DATE 17 FEB 2016**

- NOTES.

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION A DOES NOT INCLUDE MOLD

- FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.

DIMENSION B DOES NOT INCLUDE

- INTERLEAD FLASH OR PROTRUSION.

INTERLEAD FLASH OR PROTRUSION SHALL

- INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.

DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 (0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.

TERMINAL NUMBERS ARE SHOWN FOR DEEEDENIC OMITY.

- REFERENCE ONLY.

DIMENSION A AND B ARE TO BE

- DETERMINED AT DATUM PLANE -W-.

|     | MILLIMETERS |      | INC       | HES   |

|-----|-------------|------|-----------|-------|

| DIM | MIN         | MAX  | MIN       | MAX   |

| Α   | 4.90        | 5.10 | 0.193     | 0.200 |

| В   | 4.30        | 4.50 | 0.169     | 0.177 |

| С   |             | 1.20 |           | 0.047 |

| D   | 0.05        | 0.15 | 0.002     | 0.006 |

| F   | 0.50        | 0.75 | 0.020     | 0.030 |

| G   | 0.65 BSC    |      | 0.026 BSC |       |

| Н   | 0.50        | 0.60 | 0.020     | 0.024 |

| J   | 0.09        | 0.20 | 0.004     | 0.008 |

| J1  | 0.09        | 0.16 | 0.004     | 0.006 |

| K   | 0.19        | 0.30 | 0.007     | 0.012 |

| K1  | 0.19        | 0.25 | 0.007     | 0.010 |

| L   | 6.40 BSC    |      | 0.252     | BSC   |

| М   | o o         | ρ °  | 0 °       | 8 °   |

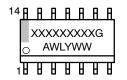

#### **GENERIC MARKING DIAGRAM\***

= Assembly Location

L = Wafer Lot = Year = Work Week W

= Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "■", may or may not be present. Some products may not follow the Generic Marking.

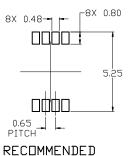

#### **RECOMMENDED SOLDERING FOOTPRINT\***

| -           | 7.06                    |

|-------------|-------------------------|

| 1           |                         |

|             |                         |

|             |                         |

|             | -                       |

|             |                         |

| J           | PITCH                   |

| 14X<br>0.36 | _==+                    |

| 0.36 - 1.26 | DIMENSIONS: MILLIMETERS |

\*For additional information on our Pb-Free strategy and soldering details, please download the onsemi Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER: | 98ASH70246A | Electronic versions are uncontrolled except when accessed directly from Printed versions are uncontrolled except when stamped "CONTROLLED" |             |

|------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | TSSOP-14 WB |                                                                                                                                            | PAGE 1 OF 1 |

onsemi and ONSEMI. are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. **onsemi** makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, Onsemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase

#### ADDITIONAL INFORMATION

**TECHNICAL PUBLICATIONS:**

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales