**Documents**

LMK04828-EP

SNAS703 - APRIL 2017

# LMK04828-EP Ultra-Low-Noise, JESD204B-Compliant Clock Jitter Cleaner

## **Features**

- **EP Features**

- Gold Bondwires

- Temperature Range: -55 to +105 °C

- Lead Finish SnPb

- Maximum Distribution Frequency: 3.2 GHz

- JESD204B Support

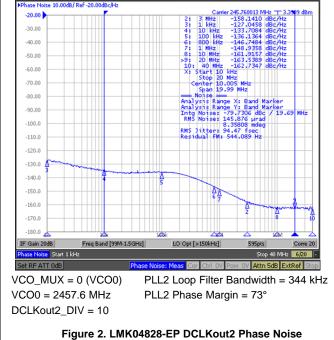

- Ultra-Low RMS Jitter

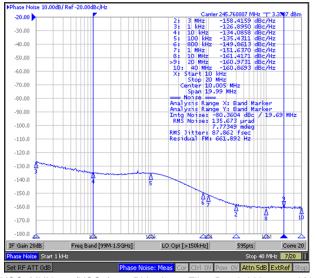

- 88-fs RMS Jitter (12 kHz to 20 MHz)

- 91-fs RMS Jitter (100 Hz to 20 MHz)

- 162.5 dBc/Hz Noise Floor at 245.76 MHz

- Up to 14 Differential Device Clocks From PLL2

- Up to 7 SYSREF Clocks

- Maximum Clock Output Frequency 3.2 GHz

- LVPECL, LVDS, HSDS, LCPECL Programmable Outputs From PLL2

- Up to 1 Buffered VCXO/Crystal Output From PLL1

- LVPECL, LVDS, 2xLVCMOS Programmable

- Multi-Mode: Dual PLL, Single PLL, and Clock Distribution

- Dual Loop PLLatinum™ PLL Architecture

- PLL1

- Up to 3 Redundant Input Clocks

- Automatic and Manual Switchover Modes

- Hitless Switching and LOS

- Integrated Low-Noise Crystal Oscillator Circuit

- Holdover Mode When Input Clocks are Lost

- PLL2

- Normalized [1 Hz] PLL Noise Floor of -227 dBc/Hz

- Phase Detector Rate up to 155 MHz

- OSCin Frequency-Doubler

- Two Integrated Low-Noise VCOs

- 50% Duty Cycle Output Divides, 1 to 32 (Even and Odd)

- Precision Digital Delay, Dynamically Adjustable

- 25-ps Step Analog Delay

- 3.15-V to 3.45-V Operation

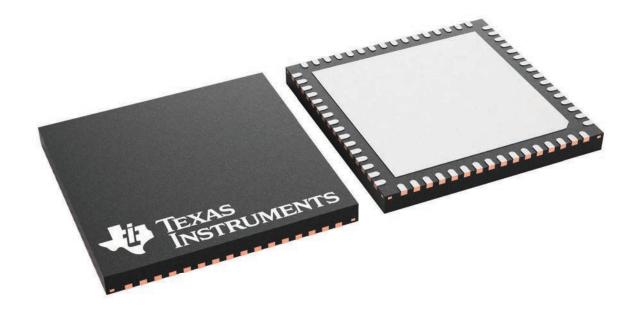

- Package: 64-Pin WQFN (9.0 mm × 9.0 mm × 0.8 mm)

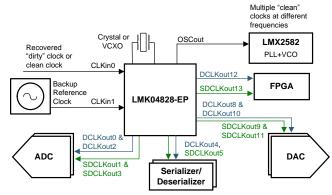

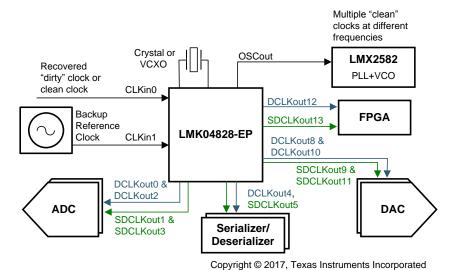

# 2 Applications

- Wireless Infrastructure

- **Data Converter Clocking**

- Networking, SONET/SDH, DSLAM

- Medical / Video / Military / Aerospace

- Test and Measurement

# Description

The LMK04828-EP device is the industry's highest performance clock conditioner with JESD204B support.

The 14 clock outputs from PLL2 can be configured to drive seven JESD204B converters or other logic devices using device and SYSREF clocks. SYSREF can be provided using both DC and AC coupling. Not limited to JESD204B applications, each of the 14 outputs can be individually configured as highperformance outputs for traditional clocking systems.

The high performance combined with features like the ability to trade off between power or performance, dual VCOs, dynamic digital delay, holdover, and glitchless analog delay make the LMK04828-EP ideal for providing flexible high-performance clocking trees.

# Device Information<sup>(1)</sup>

| PART<br>NUMBER | VCO0<br>FREQUENCY | VCO1 FREQUENCY   |

|----------------|-------------------|------------------|

| LMK04828-EP    | 2450 to 2755 MHz  | 2875 to 3080 MHz |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

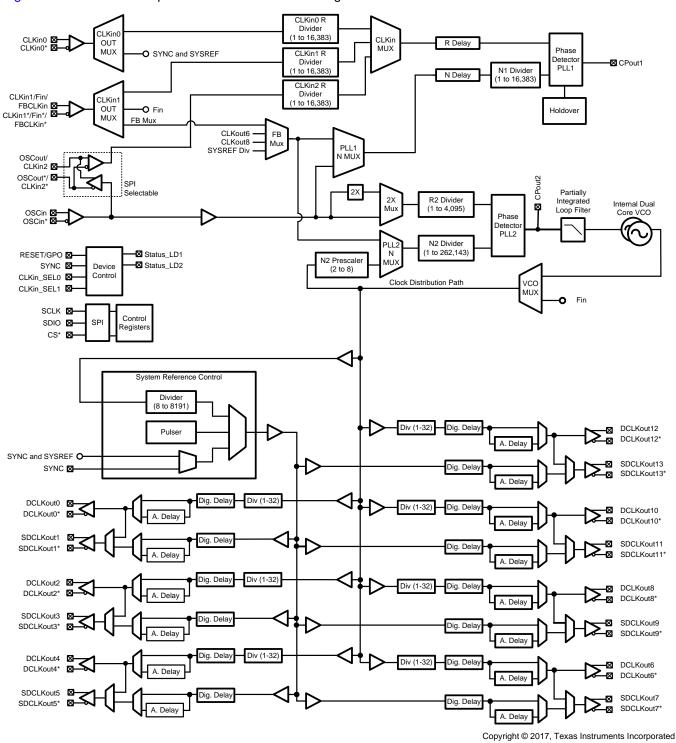

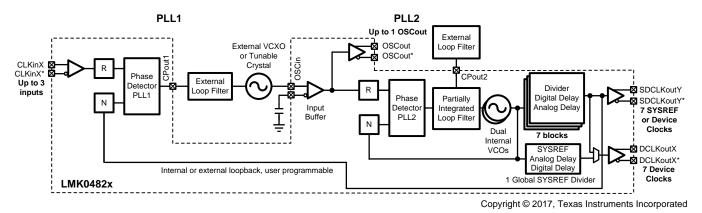

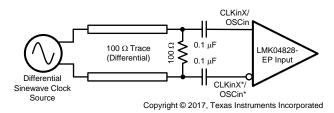

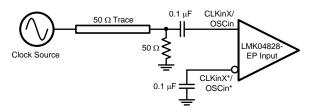

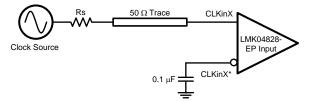

## Simplified Schematic

Copyright @ 2017, Texas Instruments Incorporated

# **Table of Contents**

| 1 | Features 1                                                    | 9.4 Device Functional Modes3                               | 34             |

|---|---------------------------------------------------------------|------------------------------------------------------------|----------------|

| 2 | Applications 1                                                | 9.5 Programming 3                                          | 37             |

| 3 | Description 1                                                 | 9.6 Register Maps3                                         | 38             |

| 4 | Revision History2                                             | 9.7 Device Register Descriptions 4                         | 12             |

| 5 | Device Comparison Table3                                      | 10 Applications and Implementation 8                       | 4              |

| 6 | Pin Configuration and Functions                               | 10.1 Application Information 8                             | 34             |

| 7 | Specifications5                                               | 10.2 Typical Application 8                                 | 37             |

| • | 7.1 Absolute Maximum Ratings 5                                | 10.3 Do's and Don'ts9                                      | )O             |

|   | 7.2 ESD Ratings                                               | 11 Power Supply Recommendations 9                          | 1              |

|   | 7.3 Recommended Operating Conditions 5                        | 11.1 Current Consumption / Power Dissipation Calculations9 | <del>)</del> 1 |

|   | 7.4 Thermal Information                                       | 12 Layout 9                                                | 2              |

|   | 7.5 Electrical Characteristics                                | 12.1 Layout Guidelines9                                    |                |

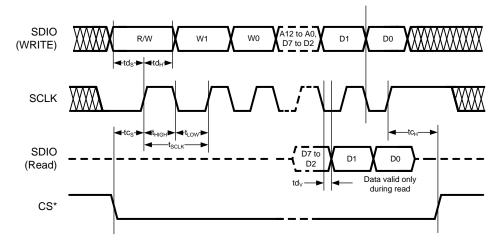

|   | 7.6 SPI Interface Timing                                      | 12.2 Layout Example9                                       |                |

|   | 7.7 Timing Diagram                                            | 13 Device and Documentation Support 9                      |                |

|   | 7.8 Typical Characteristics – Clock Output AC Characteristics | 13.1 Device Support9                                       |                |

| 8 |                                                               | 13.2 Receiving Notification of Documentation Updates 9     |                |

| 0 | Parameter Measurement Information                             | 13.3 Community Resources 9                                 |                |

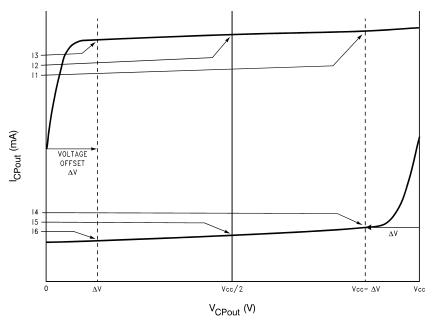

|   | 8.1 Charge Pump Current Specification Definitions 15          | 13.4 Trademarks 9                                          |                |

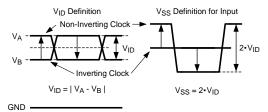

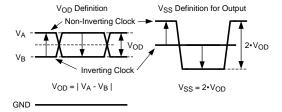

| _ | 8.2 Differential Voltage Measurement Terminology 16           | 13.5 Electrostatic Discharge Caution 9                     | )4             |

| 9 | Detailed Description                                          | 13.6 Glossary9                                             |                |

|   | 9.1 Overview                                                  | 14 Mechanical, Packaging, and Orderable                    |                |

|   | 9.2 Functional Block Diagram                                  | Information9                                               | )4             |

|   | 9.3 Feature Description24                                     |                                                            |                |

# 4 Revision History

| DATE       | REVISION | NOTES           |

|------------|----------|-----------------|

| April 2017 | *        | Initial release |

Submit Documentation Feedback

# 5 Device Comparison Table

# **Table 1. Device Configuration Information**

| PART NUMBER | REFERENC<br>E<br>INPUTS <sup>(1)</sup> | OSCout (BUFFERED OSCin<br>Clock) LVDS/ LVPECL/<br>LVCMOS (1) | PLL2 PROGRAMMABLE<br>LVDS/LVPECL/HSDS<br>OUTPUTS | VCO0 FREQUENCY   | VCO1 FREQUENCY   |

|-------------|----------------------------------------|--------------------------------------------------------------|--------------------------------------------------|------------------|------------------|

| LMK04828-EP | Up to 3                                | Up to 1                                                      | 14                                               | 2450 to 2755 MHz | 2875 to 3080 MHz |

<sup>(1)</sup> OSCout may also be third clock input, CLKin2.

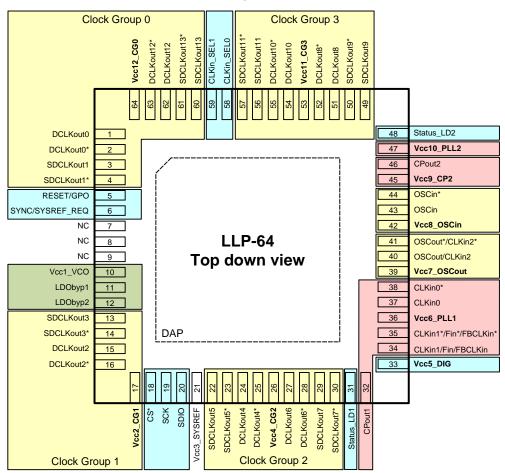

# 6 Pin Configuration and Functions

#### NKD Package 64-Pin WQFN Top View

# **Pin Functions**

| PIN |                          | I/O | TYPE         | DESCRIPTION <sup>(1)</sup>      |

|-----|--------------------------|-----|--------------|---------------------------------|

| NO. | NAME                     | 1/0 | ITE          | DESCRIPTION. /                  |

| 1 2 | DCLKout0,<br>DCLKout0*   | 0   | Programmable | Device clock output 0           |

| 3 4 | SDCLKout1,<br>SDCLKout1* | 0   | Programmable | SYSREF or device clock output 1 |

| 5   | RESET/GPO                | 1   | CMOS         | Device reset input or GPO       |

(1) See Pin Connection Recommendations for recommended connections.

# Pin Functions (continued)

|           | PIN                                |     |               |                                                                      |  |  |

|-----------|------------------------------------|-----|---------------|----------------------------------------------------------------------|--|--|

| NO.       | NAME                               | 1/0 | TYPE          | DESCRIPTION <sup>(1)</sup>                                           |  |  |

| 6         | SYNC/SYSREF_REQ                    | ı   | CMOS          | Synchronization input or SYSREF_REQ for requesting continuous SYSREF |  |  |

| 7, 8, 9   | NC                                 |     |               | Do not connect. These pins must be left floating.                    |  |  |

| 10        | Vcc1_VCO                           |     | PWR           | Power supply for VCO LDO                                             |  |  |

| 11        | LDObyp1                            |     | ANLG          | LDO bypass, bypassed to ground with 10-µF capacitor.                 |  |  |

| 12        | LDObyp2                            |     | ANLG          | LDO bypass, bypassed to ground with a 0.1-µF capacitor.              |  |  |

| 13<br>14  | SDCLKout3,<br>SDCLKout3*           | 0   | Programmable  | SYSREF or device clock output 3                                      |  |  |

| 15<br>16  | DCLKout2,<br>DCLKout2*             | 0   | Programmable  | Device clock output 2                                                |  |  |

| 17        | Vcc2_CG1                           |     | PWR           | Power supply for clock outputs 2 and 3                               |  |  |

| 18        | CS*                                | I   | CMOS          | Chip select                                                          |  |  |

| 19        | SCK                                | I   | CMOS          | SPI clock                                                            |  |  |

| 20        | SDIO                               | I/O | CMOS          | SPI data                                                             |  |  |

| 21        | Vcc3_SYSREF                        |     | PWR           | Power supply for SYSREF divider and SYNC                             |  |  |

| 22<br>23  | SDCLKout5,<br>SDCKLout5*           | 0   | Programmable  | <u>'</u>                                                             |  |  |

| 24<br>25  | DCLKout4,<br>DCLKout4*             | 0   | Programmable  | Device clock output 4                                                |  |  |

| 26        | Vcc4_CG2                           |     | PWR           | Power supply for clock outputs 4, 5, 6 and 7                         |  |  |

| 27<br>28  | DCLKout6,<br>DCLKout6*             | 0   | Programmable  | Device clock output 6                                                |  |  |

| 29<br>30  | SDCLKout7,<br>SDCLKout7*           | 0   | Programmable  | SYSREF or device clock output 7                                      |  |  |

| 31        | Status_LD1                         | I/O | Programmable  | Programmable status pin                                              |  |  |

| 32        | CPout1                             | 0   | ANLG          | Charge pump 1 output                                                 |  |  |

| 33        | Vcc5_DIG                           |     | PWR           | Power supply for the digital circuitry                               |  |  |

|           | CLKin1, CLKin1*                    | I   | ANLG          | Reference clock Input Port 1 for PLL1                                |  |  |

| 34<br>35  | FBCLKin,<br>FBCLKin*               | I   | ANLG          | Feedback input for external clock feedback input (0-delay mode)      |  |  |

|           | Fin, Fin*                          | I   | ANLG          | External VCO input (external VCO mode)                               |  |  |

| 36        | Vcc6_PLL1                          |     | PWR           | Power supply for PLL1, charge pump 1, holdover DAC                   |  |  |

| 37<br>38  | CLKin0, CLKin0*                    | I   | ANLG          | Reference clock input port 0 for PLL1                                |  |  |

| 39        | Vcc7_OSCout                        |     | PWR           | Power supply for OSCout port                                         |  |  |

| 40        | OSCout, OSCout*                    | I/O | Programmable  | Buffered output of OSCin port                                        |  |  |

| 41        | CLKin2, CLKin2*                    | .,, | 1 Togrammable | Reference clock Input Port 2 for PLL1                                |  |  |

| 42        | Vcc8_OSCin                         |     | PWR           | Power supply for OSCin                                               |  |  |

| 43<br>44  | OSCin, OSCin*                      | I   | ANLG          | Feedback to PLL1, reference input to PLL2 — AC-coupled               |  |  |

| 45        | Vcc9_CP2                           |     | PWR           | Power supply for PLL2 charge pump                                    |  |  |

| 46        | CPout2                             | 0   | ANLG          | Charge pump 2 output                                                 |  |  |

| 47        | Vcc10_PLL2                         |     | PWR           | Power supply for PLL2                                                |  |  |

| 48        | Status_LD2                         | I/O | Programmable  | Programmable status pin                                              |  |  |

| 49<br>50  | SDCLKout9,<br>SDCLKout9*           | 0   | Programmable  | SYSREF or device clock 9                                             |  |  |

| 51<br>52  | DCLKout8,<br>DCLKout8*             | 0   | Programmable  | Device clock output 8                                                |  |  |

| 53        | Vcc11_CG3                          |     | PWR           | Power supply for clock outputs 8, 9, 10, and 11                      |  |  |

| 54<br>55  | DCLKout10,<br>DCLKout10*           | 0   | Programmable  | Device clock output 10                                               |  |  |

| 56<br>57  | SDCLKout11,<br>SDCLKout11*         | 0   | Programmable  | SYSREF or device clock output 11                                     |  |  |

| 58        | CLKin_SEL0                         | I/O | Programmable  | Programmable status pin                                              |  |  |

| 59        | CLKin_SEL1                         | I/O | Programmable  | Programmable status pin                                              |  |  |

| 60        | SDCLKout13,                        | 0   | Programmable  | SYSREF or device clock output 13                                     |  |  |

| 61<br>62  | SDCLKout13*  DCLKout12, DCLKout13* | 0   | Programmable  | Device clock output 12                                               |  |  |

| 63        | DCLKout12*                         | -   | · ·           | · ·                                                                  |  |  |

| 64<br>DAD | Vcc12_CG0                          |     | PWR           | Power supply for clock outputs 0, 1, 12, and 13                      |  |  |

| DAP       | DAP                                |     | GND           | DIE ATTACH PAD, connect to GND                                       |  |  |

Submit Documentation Feedback

# **Specifications**

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                  |                                                                                  | MIN  | MAX                     | UNIT |

|------------------|----------------------------------------------------------------------------------|------|-------------------------|------|

| V <sub>CC</sub>  | Supply voltage (2)                                                               | -0.3 | 3.6                     | V    |

| $V_{IN}$         | Input voltage                                                                    | -0.3 | (V <sub>CC</sub> + 0.3) | V    |

| $T_L$            | Lead temperature (solder 4 seconds)                                              |      | 260                     | °C   |

| TJ               | Junction temperature                                                             |      | 150                     | °C   |

| I <sub>IN</sub>  | Differential input current (CLKinX/X*, OSCin/OSCin*, FBCLKin/FBCLKin*, Fin/Fin*) |      | ±5                      | mA   |

| MSL              | Moisture sensitivity level                                                       |      | 3                       |      |

| T <sub>stg</sub> | Storage temperature                                                              | -65  | 150                     | °C   |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±250  | V    |

|                    |                         | Machine Model (MM)                                                  | ±150  |      |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions. Pins listed as ±200 V may actually have higher performance.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                      | MIN  | NOM | MAX  | UNIT |

|-----------------|----------------------|------|-----|------|------|

| $T_J$           | Junction temperature |      |     | 125  | °C   |

| T <sub>A</sub>  | Ambient temperature  | -55  | 25  | 105  | °C   |

| V <sub>CC</sub> | Supply voltage       | 3.15 | 3.3 | 3.45 | V    |

Never to exceed 3.6 V.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions. Pins listed as ±250 V may actually have higher performance.

# RUMENTS

#### 7.4 Thermal Information

|                      |                                                             | LMK04828-EP |      |

|----------------------|-------------------------------------------------------------|-------------|------|

|                      | THERMAL METRIC(1)                                           | NKD (WQFN)  | UNIT |

|                      |                                                             | 64 PINS     |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance (2)                  | 24.3        | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance (3)               | 6.1         | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance <sup>(4)</sup>         | 3.5         | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter <sup>(5)</sup>   | 0.1         | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter <sup>(6)</sup> | 3.5         | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | 0.7         | °C/W |

- (1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

- The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, High-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDECstandard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- (4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- The junction-to-top characterization parameter,  $\Psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted

- from the simulation data for obtaining  $R_{\theta JA}$ , using a procedure described in JESD51-2a (sections 6 and 7). The junction-to-board characterization parameter,  $\Psi_{JB}$  estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $R_{\theta,IA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

- The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

#### 7.5 Electrical Characteristics

$(3.15 \text{ V} < \text{V}_{CC} < 3.45 \text{ V}, -55 ^{\circ}\text{C} < \text{T}_{A} < +105 ^{\circ}\text{C}$ . Typical values at  $\text{V}_{CC} = 3.3 \text{ V}, \text{T}_{A} = 25 ^{\circ}\text{C}$ , at the recommended operating conditions and are *not* assured.)

|                                                                                                                                                                 | PARAMETER                                                      | TEST CONDITIONS                                                                    | MIN   | TYP | MAX             | UNIT |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------|-------|-----|-----------------|------|

| CURRENT CO                                                                                                                                                      | NSUMPTION                                                      |                                                                                    |       |     |                 |      |

| I <sub>CC_PD</sub>                                                                                                                                              | Power-down supply current                                      |                                                                                    |       | 1   | 3               | mA   |

| I <sub>CC_CLKS</sub>                                                                                                                                            | Supply current <sup>(1)</sup>                                  | 14 HSDS 8 mA clocks enabled PLL1 and PLL2 locked.                                  |       | 565 | 670             | mA   |

| CLKin0/0*, CL                                                                                                                                                   | Kin1/1*, and CLKin2/2* INPUT CLOCK SF                          | PECIFICATIONS                                                                      | ·     |     |                 |      |

| f <sub>CLKin</sub>                                                                                                                                              | Clock input frequency                                          |                                                                                    | 0.001 |     | 750             | MHz  |

| SLEW <sub>CLKin</sub>                                                                                                                                           | Clock input slew rate (2)                                      | 20% to 80%                                                                         | 0.15  | 0.5 |                 | V/ns |

| $V_{\text{ID}}$ CLKin                                                                                                                                           | Differential clock input voltage (3)                           | AC coupled                                                                         | 0.125 |     | 1.55            | V    |

| V <sub>SS</sub> CLKin                                                                                                                                           | See Figure 4                                                   | AC-coupled                                                                         | 0.25  |     | 3.1             | Vpp  |

| V <sub>SS</sub> CLKin<br>V <sub>CLKin</sub>                                                                                                                     | Clock input<br>Single-ended input voltage                      | AC-coupled to CLKinX;<br>CLKinX* AC-coupled to Ground<br>CLKinX_TYPE = 0 (Bipolar) | 0.25  |     | 2.4             | Vpp  |

| V <sub>CLKin</sub>                                                                                                                                              |                                                                | AC-coupled to CLKinX;<br>CLKinX* AC-coupled to Ground<br>CLKinX_TYPE = 1 (MOS)     | 0.35  |     | 2.4             | Vpp  |

| V <sub>CLKin</sub>                                                                                                                                              | DC offset voltage between                                      | Each pin is AC-coupled, CLKin0/1/2<br>CLKinX_TYPE = 0 (Bipolar)                    |       | 0   |                 | mV   |

| $ V_{\text{CLKinX-offset}} $                                                                                                                                    | CLKinX/CLKinX* (CLKinX* - CLKinX)                              | Each pin is AC-coupled, CLKin0/1<br>CLKinX_TYPE = 1 (MOS)                          |       | 55  |                 | mV   |

| CLKin0/0*, CLKin  SLEW <sub>CLKin</sub> V <sub>ID</sub> CLKin  V <sub>SS</sub> CLKin  V <sub>CLKin</sub> V <sub>CLKin</sub> V <sub>CLKin</sub> -V <sub>IH</sub> | DC offset voltage between<br>CLKin2/CLKin2* (CLKin2* - CLKin2) | Each pin is AC-coupled<br>CLKinX_TYPE = 1 (MOS)                                    |       | 20  |                 | mV   |

| V <sub>CLKin-</sub> V <sub>IH</sub>                                                                                                                             | High input voltage                                             | DC-coupled to CLKinX;                                                              | 2     |     | V <sub>CC</sub> | V    |

| V <sub>CLKin</sub> – V <sub>IL</sub>                                                                                                                            | Low input voltage                                              | CLKinX* AC-coupled to Ground CLKinX_TYPE = 1 (MOS)                                 | 0     |     | 0.4             | V    |

- (1) See the applications section of *Power Supply Recommendations* for I<sub>CC</sub> for specific part configuration and how to calculate I<sub>CC</sub> for a specific design.

- To meet the jitter performance listed in the subsequent sections of this data sheet, the minimum recommended slew rate for all input clocks is 0.5 V/ns. This is especially true for single-ended clocks. Phase noise performance will begin to degrade as the clock input slew rate is reduced. However, the device functions at slew rates down to the minimum listed. When compared to single-ended clocks, differential clocks (LVDS, LVPECL) will be less susceptible to degradation in phase noise performance at lower slew rates due to their common mode noise rejection. However, it is also recommended to use the highest possible slew rate for differential clocks to achieve optimal phase noise performance at the device outputs.

- See Differential Voltage Measurement Terminology for definition of V<sub>ID</sub> and V<sub>OD</sub> voltages.

# **Electrical Characteristics (continued)**

$(3.15~V < V_{CC} < 3.45~V, -55~^{\circ}C < T_{A} < +105^{\circ}C.$  Typical values at  $V_{CC} = 3.3~V, T_{A} = 25~^{\circ}C,$  at the recommended operating conditions and are *not* assured.)

|                                       | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TEST CONDITIONS                                                                 | MIN   | TYP    | MAX  | UNIT        |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------|--------|------|-------------|

| FBCLKin/FBCLI                         | Kin* and Fin/Fin* INPUT SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <u> </u>                                                                        | l l   |        |      |             |

| f <sub>FBCLKin</sub>                  | Clock input frequency for 0-delay with external feedback.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | AC-coupled<br>CLKinX_TYPE = 0 (Bipolar)                                         | 0.001 |        | 750  | MHz         |

| £                                     | Clock input frequency for external VCO mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | AC-coupled <sup>(4)</sup><br>CLKinX_TYPE = 0 (Bipolar)                          | 0.001 |        | 3100 | MU          |

| f <sub>Fin</sub>                      | Clock input frequency for distribution mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | AC-coupled<br>CLKinX_TYPE = 0 (Bipolar)                                         | 0.001 |        | 3200 | MHz         |

| V <sub>FBCLKin/Fin</sub>              | Single-ended clock input voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | AC-coupled<br>CLKinX_TYPE = 0 (Bipolar)                                         | 0.25  |        | 2    | Vpp         |

| SLEW <sub>FBCLKin/Fin</sub>           | Slew rate on CLKin (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | AC-coupled; 20% to 80%; (CLKinX_TYPE = 0)                                       | 0.15  | 0.5    |      | V/ns        |

| PLL1 SPECIFIC                         | ATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                 | ·     |        | •    |             |

| f <sub>PD1</sub>                      | PLL1 phase detector frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                 |       |        | 40   | MHz         |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>CPout1</sub> = V <sub>CC</sub> /2, PLL1_CP_GAIN = 0                      |       | 50     |      |             |

|                                       | PLL1 charge pump source current <sup>(5)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V <sub>CPout1</sub> = V <sub>CC</sub> /2, PLL1_CP_GAIN = 1                      |       | 150    |      |             |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>CPout1</sub> = V <sub>CC</sub> /2, PLL1_CP_GAIN = 2                      |       | 250    |      |             |

| I <sub>CPout1</sub> SOURCE            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                 |       |        |      | μA          |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>CPout1</sub> = V <sub>CC</sub> /2, PLL1_CP_GAIN = 14                     |       | 1450   |      |             |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>CPout1</sub> = V <sub>CC</sub> /2, PLL1_CP_GAIN = 15                     |       | 1550   |      |             |

|                                       | PLL1 Charge pump sink current <sup>(5)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | V <sub>CPout1</sub> =V <sub>CC</sub> /2, PLL1_CP_GAIN = 0                       |       | -50    |      |             |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>CPout1</sub> =V <sub>CC</sub> /2, PLL1_CP_GAIN = 1                       |       | -150   |      |             |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>CPout1</sub> =V <sub>CC</sub> /2, PLL1_CP_GAIN = 2                       |       | -250   |      |             |

| I <sub>CPout1</sub> SINK              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                 |       |        |      | μΑ          |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>CPout1</sub> =V <sub>CC</sub> /2, PLL1_CP_GAIN = 14                      |       | -1450  |      |             |

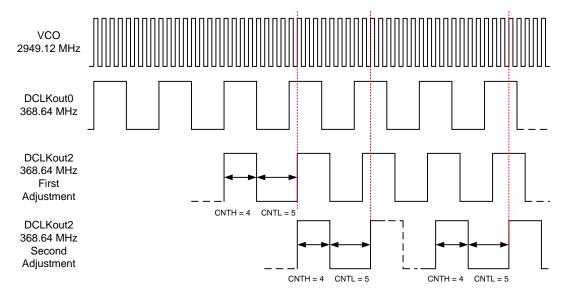

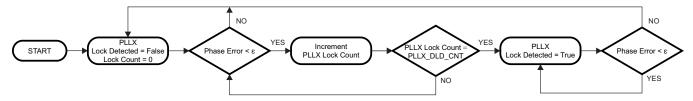

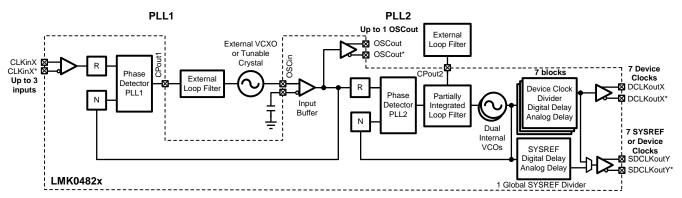

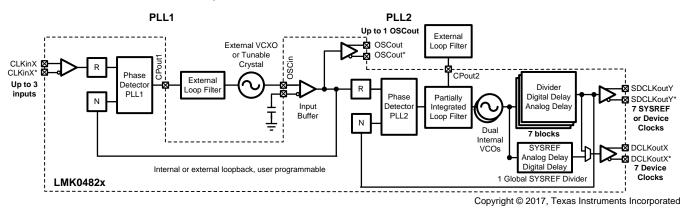

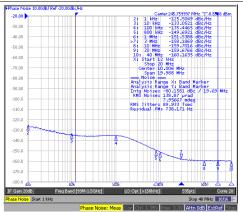

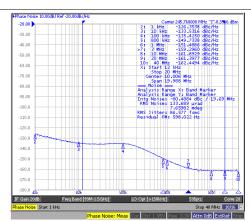

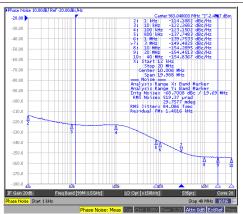

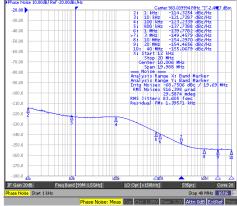

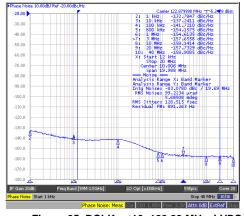

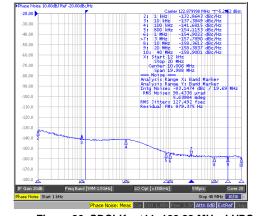

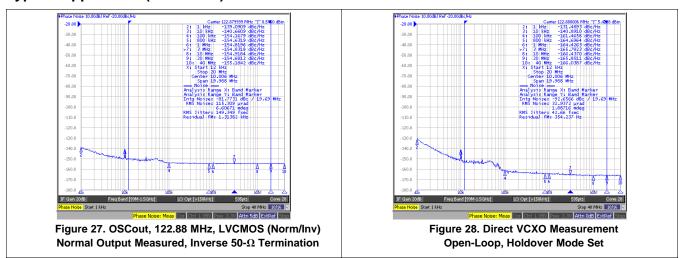

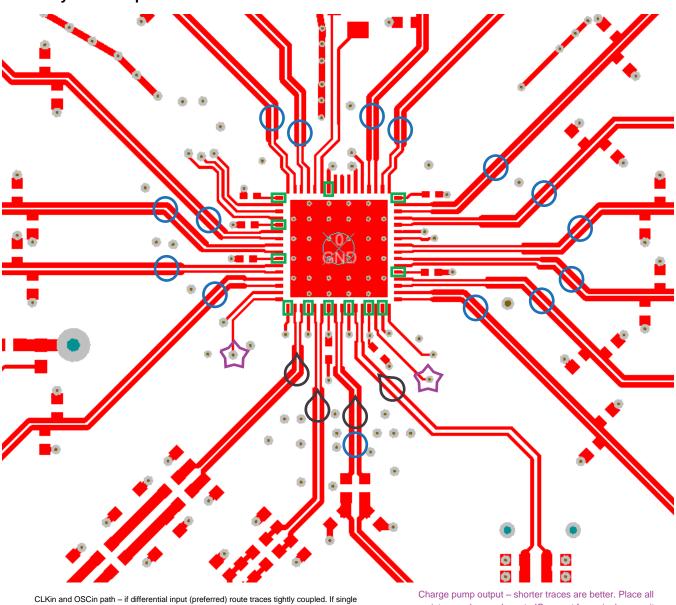

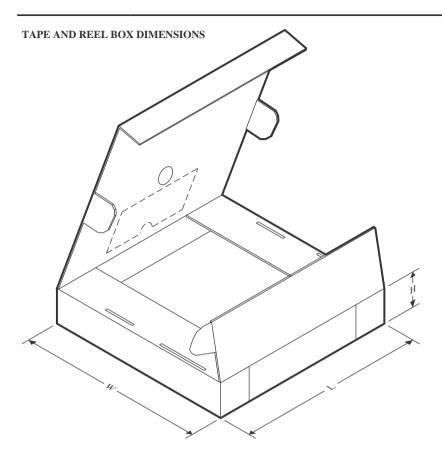

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>CPout1</sub> =V <sub>CC</sub> /2, PLL1_CP_GAIN = 15                      |       | -1550  |      |             |