# onsemi

# **3.3 V Differential Multipoint Low Voltage M-LVDS Driver Receiver**

# **NB3N200S**

#### Description

The NB3N200 is a pure 3.3 V supply differential Multipoint Low Voltage (M–LVDS) line Driver and Receiver. NB3N200S is TIA/EIA–899 compliant. NB3N200S offers the Type 1 receiver threshold at 0.0 V.

These devices has a Type-1 receiver that detect the bus state with as little as 50 mV of differential input voltage over a common-mode voltage range of -1 V to 3.4 V. The Type-1 receivers have near zero thresholds ( $\pm$ 50 mV) and exhibit 25 mV of differential input voltage hysteresis to prevent output oscillations with slowly changing signals or loss of input.

NB3N200S supports Simplex or Half Duplex bus configurations.

# Features

- Low–Voltage Differential 30  $\Omega$  to 55  $\Omega$  Line Drivers and Receivers for Signaling Rates Up to 200 Mbps

- Type-1 Receivers Incorporate 25 mV of Hysteresis

- Meets or Exceeds the M–LVDS Standard TIA/EIA–899 for Multipoint Data Interchange

- Controlled Driver Output Voltage Transition Times for Improved Signal Quality

- -1 V to 3.4 V Common–Mode Voltage Range Allows Data Transfer With up to 2 V of Ground Noise

- Bus Pins High Impedance When Disabled or  $V_{CC} \le 1.5 \text{ V}$

- M-LVDS Bus Power Up/Down Glitch Free

- Operating range:  $V_{CC} = 3.3 \pm 10\% V(3.0 \text{ to } 3.6 \text{ V})$

- Operation from -40°C to 85°C.

- Pb–Free SOIC 8 Package

- These are Pb-Free Devices

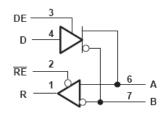

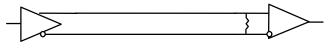

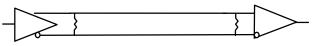

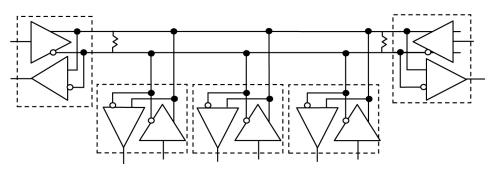

Figure 1. Logic Diagrams

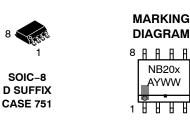

| NB20x  | = Specific Device Code |

|--------|------------------------|

| х      | = 0, 2, 4, 5           |

| А      | = Assembly Location    |

| Y      | = Year                 |

| WW     | = Work Week            |

| G or ∎ | = Pb-Free Package      |

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 17 of this data sheet.

# Applications

- Low-Power High-Speed Short-Reach Alternative to TIA/EIA-485

- Backplane or Cabled Multipoint Data and Clock Transmission

- Cellular Base Stations

- Central–Office Switches

- Network Switches and Routers

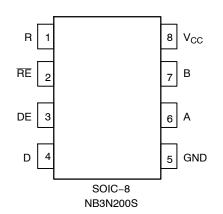

Figure 2. Pinout Diagrams (Top View)

# Table 1. PIN DESCRIPTION SOIC-8

| Number | Name | I/O Type                 | Open Default | Description                                                                                        |

|--------|------|--------------------------|--------------|----------------------------------------------------------------------------------------------------|

| 1      | R    | LVCMOS Output            |              | Receiver Output Pin                                                                                |

| 2      | RE   | LVCMOS Input             | High         | Receiver Enable Input Pin (LOW = Active, HIGH = High Z<br>Output)                                  |

| 3      | DE   | LVCMOS Input             | Low          | Driver Enable Input Pin (LOW = High Z Output, HIGH = Active)                                       |

| 4      | D    | LVCMOS Input             |              | Driver Output Pin                                                                                  |

| 5      | GND  |                          |              | Ground Supply pin. Pin must be externally connected to power supply to guarantee proper operation. |

| 6      | A    | M–LVDS Input /<br>Output |              | Transceiver Invert Input / Output Pin                                                              |

| 7      | В    | M–LVDS Input /<br>Output |              | Transceiver True Input / Output Pin                                                                |

| 8      | VCC  |                          |              | Power Supply pin. Pin must be externally connected to power supply to guarantee proper operation.  |

#### Table 2. DEVICE FUNCTION TABLE

|                           | Inputs                           |        | Output |       |

|---------------------------|----------------------------------|--------|--------|-------|

| TYPE 1 Receiver (NB3N200) | $V_{ID} = V_A - V_B$             | RE     | R      |       |

|                           | $V_{ID} \ge 50 \text{ mV}$       | L      | Н      |       |

|                           | –50 mV < V <sub>ID</sub> < 50 mV | L      | ?      |       |

|                           | V <sub>ID</sub> ≤ −50 mV         | L      | L      |       |

|                           | Х                                | Н      | Z      |       |

|                           | Х                                | Open   | Z      |       |

|                           | Open                             | L      | ?      |       |

|                           | Input                            | Enable | Output |       |

|                           | D                                | DE     | A / Y  | B / Z |

|                           | L                                | Н      | L      | Н     |

| DRIVER                    | Н                                | Н      | Н      | L     |

|                           | Open                             | Н      | L      | Н     |

|                           | Х                                | Open   | Z      | Z     |

|                           | Х                                | L      | Z      | Z     |

H = High, L = Low, Z = High Impedance, X = Don't Care, ? = Indeterminate

#### Table 3. ATTRIBUTES (Note 1)

|                                 | Characteristics                                           |                        | Value                            |

|---------------------------------|-----------------------------------------------------------|------------------------|----------------------------------|

| Internal Input Pu               | ullup Resistor                                            |                        | 50 kΩ                            |

| Internal Input Pu               | Internal Input Pulldown Resistor                          |                        | 50 kΩ                            |

| ESD<br>Protection               | Human Body Model (JEDEC<br>Standard 22, Method A114-A)    | A, B, Y, Z<br>All Pins | ±6 kV<br>±2 kV                   |

|                                 | Machine Model                                             | All Pins               | ±200 V                           |

|                                 | Charged –Device Model (JEDEC<br>Standard 22, Method C101) | All Pins               | ±1500 V                          |

| Moisture Sensit                 | ivity, Indefinite Time Out of Drypack (                   | Note 1)                | Level 1                          |

| Flammability Ra<br>Oxygen Index | Flammability Rating                                       |                        | UL-94 V-0 @ 0.125 in<br>28 to 34 |

| Transistor Coun                 | t                                                         |                        | 917 Devices                      |

| Meets or exceed                 | ds JEDEC Spec EIA/JESD78 IC Latc                          | hup Test               |                                  |

1. For additional information, see Application Note AND8003/D.

#### Table 4. MAXIMUM RATINGS (Note 2)

| Symbol           | Parameter                                | Condition 1        | Condition 2                                                                                        | Rating                                                                                  | Unit              |

|------------------|------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------|

| V <sub>CC</sub>  | Supply Voltage                           |                    |                                                                                                    | $-0.5 \leq V_{CC} \leq 4.0$                                                             | V                 |

| V <sub>IN</sub>  | Input Voltage                            | D, DE, RE          |                                                                                                    | $-0.5 \leq V_{IN} \leq 4.0$                                                             | V                 |

|                  |                                          | A, B (200, 204)    |                                                                                                    | $-1.8 \leq V_{IN} \leq 4.0$                                                             |                   |

|                  |                                          | A, B (202, 205)    |                                                                                                    | $-4.0 \leq V_{IN} \leq 6.0$                                                             |                   |

| I <sub>OUT</sub> | Output Voltage                           | R<br>Y, Z, A, B    |                                                                                                    | $\begin{array}{l} -0.3 \leq I_{OUT} \leq 4.0 \\ -1.8 \leq I_{OUT} \leq 4.0 \end{array}$ | V                 |

| Τ <sub>Α</sub>   | Operating Temperature Range, Industrial  |                    |                                                                                                    | -40 to ≤ +85                                                                            | °C                |

| T <sub>stg</sub> | Storage Temperature Range                |                    |                                                                                                    | -65 to +150                                                                             | °C                |

| $\theta_{JA}$    | Thermal Resistance (Junction-to-Ambient) | 0 lfpm<br>500 lfpm | SOIC-8                                                                                             | 190<br>130                                                                              | °C/W<br>°C/W      |

| θ <sub>JC</sub>  | Thermal Resistance (Junction-to-Case)    | (Note 3)           | SOIC-8                                                                                             | 41 to 44                                                                                | °C/W              |

| T <sub>sol</sub> | Wave Solder                              |                    |                                                                                                    | 265                                                                                     | °C                |

| P <sub>D</sub>   | Power Dissipation (Continuous)           | SOIC-8             | $\begin{array}{c} T_A = 25^\circ C\\ 25^\circ C < T_A < 85^\circ C\\ T_A = 85^\circ C \end{array}$ | 725<br>5.8<br>377                                                                       | mW<br>mW/°C<br>mW |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

2. Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and not valid simultaneously. If stress limits are exceeded device functional operation is not implied, damage may occur and reliability may be affected.

3. JEDEC standard multilayer board – 2S2P (2 signal, 2 power).

# Table 5. DC CHARACTERISTICS VCC = $3.3 \pm 10\%$ V( 3.0 to 3.6 V), GND = 0 V, T<sub>A</sub> = $-40^{\circ}$ C to $+85^{\circ}$ C (See Notes 4, 5)

| Symbol          | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Min  | Тур           | Max                 | Unit |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|---------------------|------|

| ICC             | Power Supply Current<br>Receiver Disabled Driver Enabled $\overline{\text{RE}}$ and DE at V <sub>CC</sub> , R <sub>L</sub> = 50 $\Omega$ , All others open<br>Driver and Receiver Disabled RE at VCC, DE at 0 V, R <sub>L</sub> = No Load, All others open<br>Driver and Receiver Enabled RE at 0 V, DE at V <sub>CC</sub> , R <sub>L</sub> = 50 $\Omega$ , All others open<br>Receiver Enabled Driver Disabled RE at 0 V, DE at 0 V, R <sub>L</sub> = 50 $\Omega$ , All others open |      | 13<br>1<br>16 | 22<br>4<br>24<br>13 | mA   |

| VIH             | Input HIGH Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2    |               | V <sub>CC</sub>     | V    |

| V <sub>IL</sub> | Input LOW Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | GND  |               | 0.8                 | V    |

| VBUS            | Voltage at any bus terminal VA, VB, VY or VZ                                                                                                                                                                                                                                                                                                                                                                                                                                         | -1.4 |               | 3.8                 | V    |

| VID             | Magnitude of differential input voltage                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.05 |               | V <sub>CC</sub>     |      |

DRIVER

| Symbol                                  | Characteristic                                                                                                                                        | Min                  | Тур     | Max                 | Unit |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------|---------------------|------|

| DRIVER                                  |                                                                                                                                                       |                      |         |                     |      |

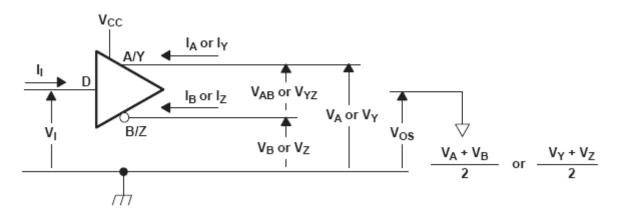

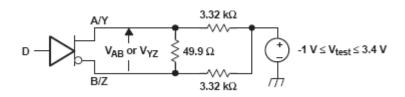

| V <sub>AB</sub>   /<br> V <sub>YZ</sub> | Differential output voltage magnitude (see Figure 4)                                                                                                  | 480                  |         | 650                 | mV   |

| $\Delta  V_{AB}  / \Delta  V_{YZ} $     | Change in Differential output voltage magnitude between logic states (see Figure 4)                                                                   | -50                  |         | 50                  | mV   |

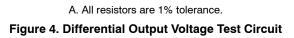

| V <sub>OS(SS)</sub>                     | Steady state common mode output voltage (see Figure 5)                                                                                                | 0.8                  |         | 1.2                 | V    |

| $\Delta V_{OS(SS)}$                     | Change in Steady state common mode output voltage between logic states (see Figure 5)                                                                 | -50                  |         | 50                  | mV   |

| V <sub>OS(PP)</sub>                     | Peak-to-peak common-mode output voltage (see Figure 5)                                                                                                |                      |         | 150                 | mV   |

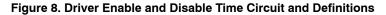

| V <sub>YOC</sub> /<br>V <sub>AOC</sub>  | Maximum steady-state open-circuit output voltage (see Figure 9)                                                                                       | 0                    |         | 2.4                 | V    |

| V <sub>ZOC</sub> /<br>V <sub>BOC</sub>  | Maximum steady-state open-circuit output voltage (see Figure 9)                                                                                       | 0                    |         | 2.4                 | V    |

| V <sub>P(H)</sub>                       | Voltage overshoot, low-to-high level output (see Figure 7)                                                                                            |                      |         | 1.2 V <sub>SS</sub> | V    |

| V <sub>P(L)</sub>                       | Voltage overshoot, high-to-low level output (see Figure 7)                                                                                            | -0.2 V <sub>SS</sub> |         |                     | V    |

| IIH                                     | High–level input current (D, DE) V <sub>IH</sub> = 2 V                                                                                                | 0                    |         | 10                  | uA   |

| Ι <sub>ΙL</sub>                         | Low–level input current (D, DE) V <sub>IL</sub> = 0.8 V                                                                                               | 0                    |         | 10                  | uA   |

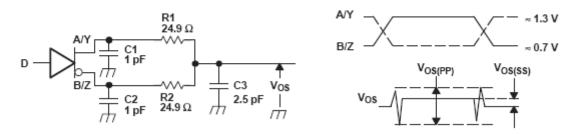

| JI <sub>OS</sub> J                      | Differential short-circuit output current magnitude (see Figure 6)                                                                                    |                      |         | 24                  | mA   |

| I <sub>OZ</sub>                         | High–impedance state output current (driver only) $-1.4 \text{ V} \le (\text{VY or VZ}) \le 3.8 \text{ V}$ , other output at 1.2 V                    | -15                  |         | 10                  | uA   |

| I <sub>O(OFF)</sub>                     | Power–off output current (0 V $\leq$ V <sub>CC</sub> $\leq$ 1.5 V)<br>–1.4 V $\leq$ (VY or VZ) $\leq$ 3.8 V, other output at 1.2 V                    | -10                  |         | 10                  | uA   |

| $C_{Y}/C_{Z}$                           | Output Capacitance VI = 0.4 sin( $30E^6\pi t$ ) + 0.5 V, other outputs at 1.2 V using HP4194A impedance analyzer (or equivalent)                      |                      | 3       |                     | pF   |

| C <sub>YZ</sub>                         | Differential Output Capacitance VAB = 0.4 sin( $30E^6\pi t$ ) V, other outputs at 1.2 V using HP4194A impedance analyzer (or equivalent)              |                      |         | 2.5                 | pF   |

| $C_{Y/Z}$                               | Output Capacitance Balance, (Cr/Cz)                                                                                                                   | 99                   |         | 101                 | %    |

| RECEIVER                                | 1                                                                                                                                                     |                      |         |                     |      |

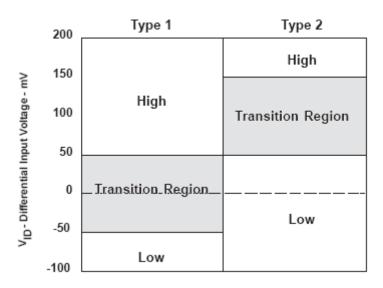

| V <sub>IT+</sub>                        | Positive-going Differential Input voltage Threshold (See Figure 11 & Table 8)<br>Type 1<br>Type 2                                                     |                      |         | 50<br>150           | mV   |

| V <sub>IT-</sub>                        | Negative-going Differential Input voltage Threshold (See Figure 11 & Table 8)<br>Type 1<br>Type 2                                                     | -50<br>50            |         |                     | mV   |

| V <sub>HYS</sub>                        | Differential Input Voltage Hysteresis (See Figure 11 and Table 2)<br>Type 1<br>Type 2                                                                 |                      | 25<br>0 |                     | mV   |

| VOH                                     | High-level output voltage (IOH = -8 mA                                                                                                                | 2.4                  |         | 1                   | V    |

| VOL                                     | Low-level output voltage (IOL = 8 mA)                                                                                                                 |                      |         | 0.4                 | V    |

| I <sub>IH</sub>                         | RE High-level input current (VIH = 2 V)                                                                                                               | -10                  |         | 0                   | μA   |

| Ι <sub>ΙL</sub>                         | RE Low-level input current (VIL = 0.8 V)                                                                                                              | -10                  |         | 0                   | μA   |

| I <sub>OZ</sub>                         | High-impedance state output current (VO = 0 V of 3.6 V)                                                                                               | -10                  |         | 15                  | μA   |

| $C_A / C_B$                             | Input Capacitance VI = 0.4 sin( $30E^6\pi t$ ) + 0.5 V, other outputs at 1.2 V using HP4194A impedance analyzer (or equivalent)                       |                      | 3       |                     | pF   |

| C <sub>AB</sub>                         | Differential Input Capacitance V <sub>AB</sub> = 0.4 sin( $30E^{6}\pi t$ ) V, other outputs at 1.2 V using HP4194A impedance analyzer (or equivalent) |                      |         | 2.5                 | pF   |

| C <sub>A/B</sub>                        | Input Capacitance Balance, (CA/CB)                                                                                                                    | 99                   |         | 101                 | %    |

#### **Table 5. DC CHARACTERISTICS** VCC = 3.3 ±10% V( 3.0 to 3.6 V), GND = 0 V, T<sub>A</sub> = -40°C to +85°C (See Notes 4, 5)

| Table 5. DC CHARACTERISTICS VCC = 3.3 ±10% | ( 3.0 to 3.6 V), GND = 0 V, T <sub>A</sub> = -40°C to +85°C (See Notes 4, 5) | ) |

|--------------------------------------------|------------------------------------------------------------------------------|---|

|--------------------------------------------|------------------------------------------------------------------------------|---|

|                      |                                                                                                                                                                                  |                 | <b>Typ</b><br>(Note |               |      |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------|---------------|------|

| Symbol               | Characteristic                                                                                                                                                                   | Min             | 5)                  | Max           | Unit |

| BUS INPU             | T AND OUTPUT                                                                                                                                                                     |                 |                     |               |      |

| I <sub>A</sub>       | Input Current Receiver or Transceiver with Driver Disabled                                                                                                                       |                 |                     |               | uA   |

|                      | $V_{A} = 3.8 \text{ V}, V_{B} = 1.2 \text{ V}$ $V_{A} = 0.0 \text{ V or } 2.4 \text{ V}, V_{B} = 1.2 \text{ V}$ $V_{A} = -1.4 \text{ V}, V_{B} = 1.2 \text{ V}$                  | 0<br>-20<br>-32 |                     | 32<br>20<br>0 |      |

| Ι <sub>Β</sub>       | Input Current Receiver or Transceiver with Driver Disabled                                                                                                                       |                 |                     |               | uA   |

|                      | $V_{B} = 3.8 V, V_{A} = 1.2 V$ $V_{B} = 0.0 V \text{ or } 2.4 V, V_{A} = 1.2 V$ $V_{B} = -1.4 V, V_{A} = 1.2 V$                                                                  | 0<br>-20<br>-32 |                     | 32<br>20<br>0 |      |

| I <sub>AB</sub>      | Differential Input Current Receiver or Transceiver with driver disabled (I <sub>A</sub> –I <sub>B</sub> ) $V_A = V_B \ , \ -1.4 \le V_A \le 3.8 \ V$                             | -4              |                     | 4             | uA   |

| I <sub>A(OFF)</sub>  | Input Current Receiver or Transceiver Power Off 0V $\leq$ V <sub>CC</sub> $\leq$ 1.5 and:                                                                                        |                 |                     |               | uA   |

|                      | $V_{A} = 3.8 \text{ V}, V_{B} = 1.2 \text{ V}$ $V_{A} = 0.0 \text{ V or } 2.4 \text{ V}, V_{B} = 1.2 \text{ V}$ $V_{A} = -1.4 \text{ V}, V_{B} = 1.2 \text{ V}$                  | 0<br>-20<br>-32 |                     | 32<br>20<br>0 |      |

| I <sub>B(OFF)</sub>  | Input Current Receiver or Transceiver Power Off 0V $\leq$ V <sub>CC</sub> $\leq$ 1.5 and:                                                                                        |                 |                     |               | uA   |

|                      | $V_{B} = 3.8 \text{ V}, V_{A} = 1.2 \text{ V}$ $V_{B} = 0.0 \text{ V or } 2.4 \text{ V}, V_{A} = 1.2 \text{ V}$ $V_{B} = -1.4 \text{ V}, V_{A} = 1.2 \text{ V}$                  | 0<br>-20<br>-32 |                     | 32<br>20<br>0 |      |

| I <sub>AB(OFF)</sub> | Receiver Input or Transceiver Input/Output Power Off Differential Input Current; (I <sub>A</sub> -I <sub>B</sub> )                                                               |                 |                     |               | uA   |

| . ,                  | $V_A$ = $V_B$ , 0 $\leq$ $V_{CC}$ $\leq$ 1.5 V, $-1.4$ $\leq$ $V_A$ $\leq$ 3.8 V                                                                                                 | -4              |                     | 4             |      |

| C <sub>A</sub>       | Transceiver Input Capacitance with Driver Disabled VA = 0.4 sin( $30E^6\pi t$ ) + 0.5 V using HP4194A impedance analyzer (or equivalent); V <sub>B</sub> = 1.2 V                 |                 | 5                   |               | pF   |

| C <sub>B</sub>       | Transceiver Input Capacitance with Driver Disabled V <sub>B</sub> = 0.4 sin( $30E^{6}\pi t$ ) + 0.5 V using HP4194A impedance analyzer (or equivalent); V <sub>A</sub> = 1.2 V   |                 | 5                   |               | pF   |

| C <sub>AB</sub>      | Transceiver Differential Input Capacitance with Driver Disabled VA = 0.4 sin( $30E^6\pi t$ ) + 0.5 V using HP4194A impedance analyzer (or equivalent);<br>V <sub>B</sub> = 1.2 V |                 |                     | 3.0           | pF   |

| C <sub>A/B</sub>     | Transceiver Input Capacitance Balance with Driver Disabled, (CA/CB)                                                                                                              | 99              |                     | 101           | %    |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm.

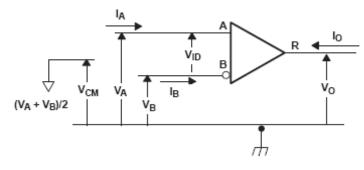

4. See Figure 3. DC Measurements reference.

5. Typ value at 25°C and 3.3 VCC supply voltage.

# Table 6. DRIVER AC CHARACTERISTICS VCC = $3.3 \pm 10\%$ V( 3.0 to 3.6 V), GND = 0 V, T<sub>A</sub> = $-40^{\circ}$ C to $+85^{\circ}$ C (Note 6)

| Symbol                              | Characteristic                                                                                                                                                             | Min | Тур | Max | Unit |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

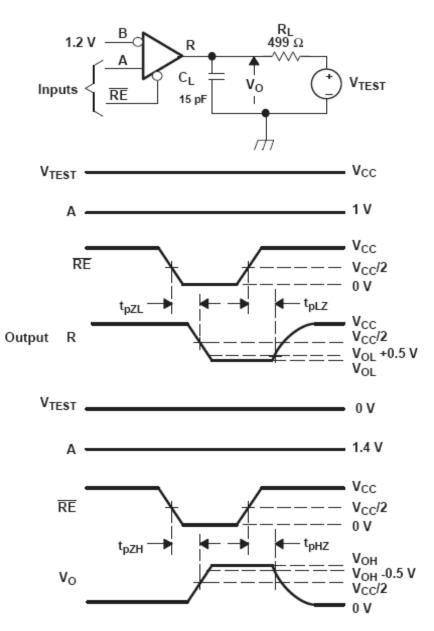

| t <sub>PLH</sub> / t <sub>PHL</sub> | Propagation Delay (See Figure 7)                                                                                                                                           | 1.0 |     | 2.4 | ns   |

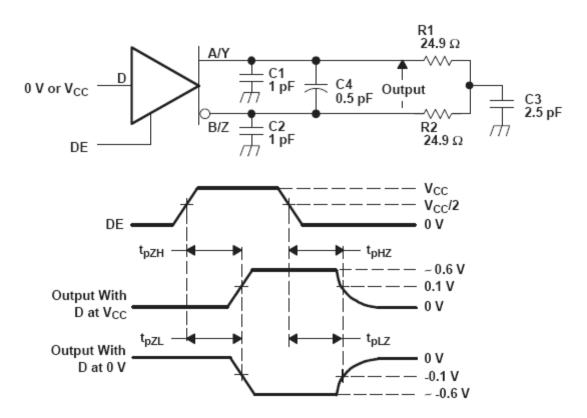

| t <sub>PHZ</sub> / t <sub>PLZ</sub> | Disable Time HIGH or LOW state to High Impedance (See Figure 8)                                                                                                            |     |     | 7   | ns   |

| t <sub>PZH</sub> / t <sub>PZL</sub> | Enable Time High Impedance to HIGH or LOW state (See Figure 8)                                                                                                             |     |     | 7   | ns   |

| t <sub>SK(P)</sub>                  | Pulse Skew ( t <sub>PLH</sub> – t <sub>PHL</sub>  ) (See Figure 7)                                                                                                         |     | 0   | 150 | ps   |

| t <sub>SK(PP)</sub>                 | Device to Device Skew similar path and conditions (See Figure 7)                                                                                                           |     |     | 0.9 | ns   |

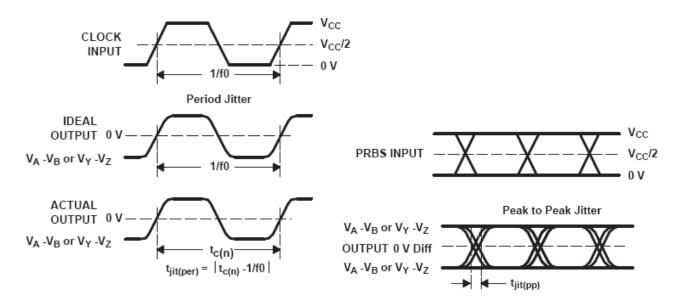

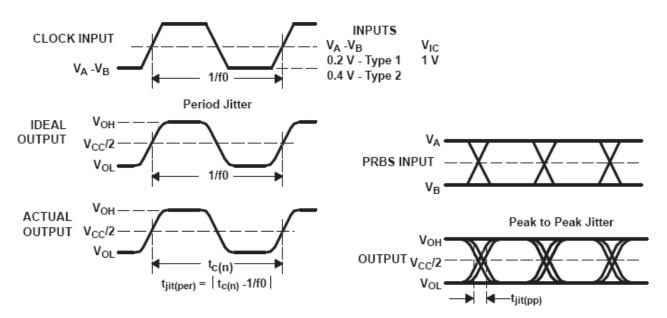

| t <sub>JIT(PER)</sub>               | Period Jitter RMS, 100 MHz (Source tr/tf 0.5 ns, 10 and 90 % points, 30k samples. Source jitter de-embedded from Output values ) (See Figure 10)                           |     |     | 3   | ps   |

| t <sub>JIT(PP)</sub>                | Peak-to-peak Jitter, 200 Mbps 2 <sup>15</sup> -1 PRBS (Source tr/tf 0.5 ns, 10 and 90% points, 100k samples. Source jitter de-embedded from Output values) (See Figure 10) |     |     | 150 | ps   |

| tr / tf                             | Differential Output rise and fall times (See Figure 7)                                                                                                                     | 1   |     | 1.6 | ns   |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm.

6. Typ value at 25°C and 3.3  $V_{CC}$  supply voltage.

| Symbol                              | Characteristic                                                                                                                                                                                                                                                  | Min | Тур        | Max        | Unit |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|------------|------|

| t <sub>PLH</sub> / t <sub>PHL</sub> | Propagation Delay (See Figure 12)                                                                                                                                                                                                                               | 2   | 4          | 6          | ns   |

| t <sub>PHZ</sub> / t <sub>PLZ</sub> | Disable Time HIGH or LOW state to High Impedance (See Figure 13)                                                                                                                                                                                                |     |            | 10         | ns   |

| t <sub>PZH</sub> / t <sub>PZL</sub> | Enable Time High Impedance to HIGH or LOW state (See Figure 13)                                                                                                                                                                                                 |     |            | 15         | ns   |

| t <sub>SK(P)</sub>                  | Pulse Skew ( t <sub>PLH</sub> – t <sub>PHL</sub>  ) (See Figure 12) C <sub>L</sub> = 5 pF<br>Type 1<br>Type 2                                                                                                                                                   |     | 100<br>300 | 300<br>500 | ps   |

| t <sub>SK(PP)</sub>                 | Device to Device Skew similar path and conditions (See Figure 12) $C_L = 5 \text{ pF}$                                                                                                                                                                          |     |            | 1          | ns   |

| t <sub>JIT(PER)</sub>               | Period Jitter RMS, 100 MHz (Source: VID = 200 mV <sub>pp</sub> for 201 and 203, VID = 400 mV <sub>pp</sub> for 206 and 207, V <sub>CM</sub> =1 V, tr/tf 0.5 ns, 10 and 90 % points, 30k samples. Source jitter de–embedded from Output values ) (See Figure 14) |     | 4          | 7          | ps   |

| t <sub>JIT(PP)</sub>                | Peak-to-peak Jitter, 200 Mbps 2 <sup>15</sup> -1 PRBS (Source tr/tf 0.5 ns, 10% and 90% points,<br>100k samples. Source jitter de-embedded from Output values) (See Figure 14)<br>Type 1<br>Type 2                                                              |     | 300<br>450 | 700<br>800 | ps   |

| tr / tf                             | Differential Output rise and fall times (See Figure 12) $C_L = 15 \text{ pF}$                                                                                                                                                                                   | 1   |            | 2.3        | ns   |

7. Typ value at 25°C and 3.3 VCC supply voltage. .

# Figure 3. Driver Voltage and Current Definitions

A. All input pulses are supplied by a generator having the following characteristics: tr or tt  $\leq 1$  ns, pulse frequency = 500 kHz, duty cycle =  $50 \pm 5\%$ .

B. C1, C2 and C3 include instrumentation and fixture capacitance within 2 cm of the D.U.T. and are 20% tolerance.

C. R1 and R2 are metal film, surface mount, 1% tolerance, and located within 2 cm of the D.U.T.

D. The measurement of VOs(PP) is made on test equipment with a -3 dB bandwidth of at least 1 GHz.

#### Figure 5. Test Circuit and Definitions for the Driver Common-Mode Output Voltage

Figure 6. Driver Short-Circuit Test Circuit

A. All input pulses are supplied by a generator having the following characteristics: tr or tr $\leq$  1 ns, frequency = 500 kHz, duty cycle = 50 ±5%.

B. C1, C2, and C3 include instrumentation and fixture capacitance within 2 cm of the D.U.T. and are 20%.

C. R1 is a metal film, surface mount, and 1% tolerance and located within 2 cm of the D.U.T.

D. The measurement is made on test equipment with a -3 dB bandwidth of at least 1 GHz.

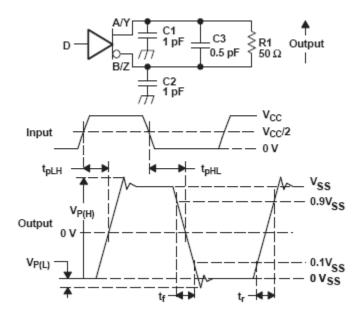

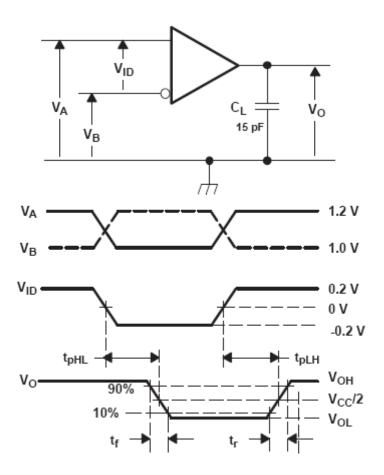

#### Figure 7. Driver Test Circuit, Timing, and Voltage Definitions for the Differential Output Signal

A. All input pulses are supplied by a generator having the following characteristics: tr or tt  $\leq$  1 ns, frequency = 500 kHz, duty cycle = 50 ±5%.

B. C1, C2, C3, and C4 includes instrumentation and fixture capacitance within 2 cm of the D.U.T. and are 20%. C. R1 and R2 are metal film, surface mount, and 1% tolerance and located within 2 cm of the D.U.T.

D. The measurement is made on test equipment with a -3 dB bandwidth of at least 1 GHz.

Figure 9. Maximum Steady State Output Voltage

A. All input pulses are supplied by an Agilent 8304A Stimulus System.

B. The measurement is made on a TEK TDS6604 running TDSJIT3 application software

C. Period jitter is measured using a 100 MHz 50  $\pm$ 1% duty cycle clock input.

D. Peak-to-peak jitter is measured using a 200 Mbps 2<sup>15</sup>-1 PRBS input.

#### Figure 10. Driver Jitter Measurement Waveforms

Figure 11. Receiver Voltage and Current Definitions

A. All input pulses are supplied by a generator having the following characteristics: tr or tr  $\leq$  1 ns, frequency = 50 MHz, duty cycle = 50  $\pm$ 5%. CL is a combination of a 20%-tolerance, low-loss ceramic, surface-mount capacitor and fixture capacitance within 2 cm of the D.U.T.

B. The measurement is made on test equipment with a -3 dB bandwidth of at least 1 GHz.

Figure 12. Receiver Timing Test Circuit and Waveforms

A. All input pulses are supplied by a generator having the following characteristics: tr or tr  $\leq 1$  ns, frequency = 500 kHz, duty cycle = 50  $\pm 5\%$ .

B. RL is 1% tolerance, metal film, surface mount, and located within 2 cm of the D.U.T.

C. CL is the instrumentation and fixture capacitance within 2 cm of the DUT and 20%.

#### Figure 13. Receiver Enable/Disable Time Test Circuit and Waveforms

A. All input pulses are supplied by an Agilent 8304A Stimulus System.

B. The measurement is made on a TEK TDS6604 running TDSJIT3 application software

C. Period jitter is measured using a 100 MHz 50  $\pm 1\%$  duty cycle clock input.

D. Peak-to-peak jitter is measured using a 200 Mbps 2<sup>15</sup>-1 PRBS input.

# Figure 14. Receiver Jitter Measurement Waveforms

| Applied Voltages |        | Resulting Differential<br>Input Voltage | Resulting Common–<br>Mode Input Voltage |                 |

|------------------|--------|-----------------------------------------|-----------------------------------------|-----------------|

| VIA              | VIB    | VID                                     | VIC                                     | Receiver Output |

| 2.400            | 0.000  | 2.400                                   | 1.200                                   | Н               |

| 0.000            | 2.400  | -2.400                                  | 1.200                                   | L               |

| 3.800            | 3.750  | 0.050                                   | 3.775                                   | Н               |

| 3.750            | 3.800  | -0.050                                  | 3.775                                   | L               |

| -1.350           | -1.400 | 0.050                                   | -1.375                                  | Н               |

| -1.400           | -1.350 | -0.050                                  | -1.375                                  | L               |

#### Table 8. TYPE-1 RECEIVER INPUT THRESHOLD TEST VOLTAGES

H = high level, L = low level, output state assumes receiver is enabled ( $\overline{RE} = L$ )

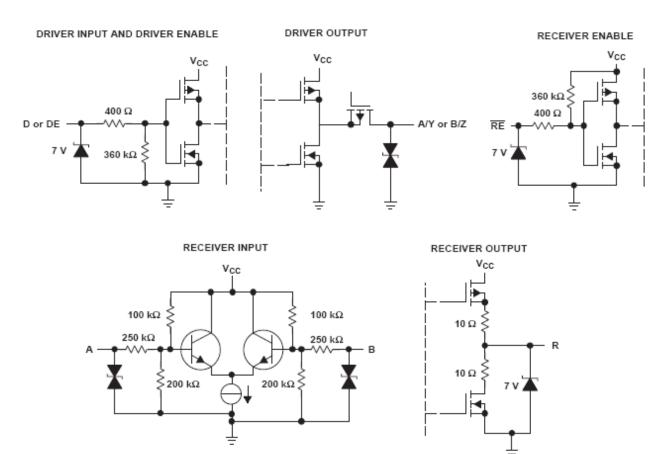

Figure 15. Equivalent Input and Output Schematic Diagrams

# **APPLICATION INFORMATION**

#### **Receiver Input Threshold (Failsafe)**

The MLVD standard defines a type 1 and type 2 receiver. Type 1 receivers include no provisions for failsafe and have their differential input voltage thresholds near zero volts. Type 2 receivers have their differential input voltage thresholds offset from zero volts to detect the absence of a voltage difference. The impact to receiver output by the offset input can be seen in Table 9 and Figure 16.

| Receiver Type | Output Low                     | Output High                  |  |

|---------------|--------------------------------|------------------------------|--|

| Type 1        | $-2.4~V \leq VID \leq -0.05~V$ | $0.05~V \leq VID \leq 2.4~V$ |  |

Figure 16. Receiver Differential Input Voltage Showing Transition Regions by Type

#### Live Insertion/Glitch-Free Power Up/Down

The NB3N200 family of products provides a glitch-free power up/down feature that prevents the M–LVDS outputs of the device from turning on during a power up or power down event. This is especially important in live insertion applications, when a device is physically connected to an M–LVDS multipoint bus and  $V_{CC}$  is ramping.

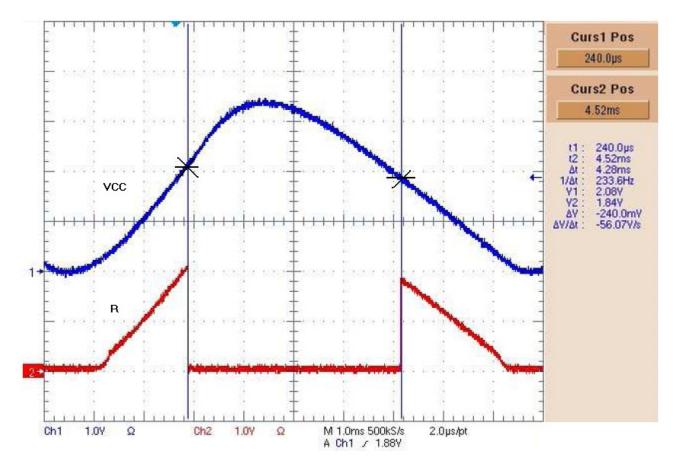

While the M–LVDS interface for these devices is glitch free on power up/down, the receiver output structure is not.

Figure 17 shows the performance of the receiver output pin, R (CHANNEL 2), as  $V_{CC}$  (CHANNEL 1) is ramped. The glitch on the R pin is independent of the RE voltage. Any complications or issues from this glitch are easily resolved in power sequencing or system requirements that suspend operation until  $V_{CC}$  has reached a steady state value.

Figure 17. M-LVDS Receiver Output: VCC (CHANNEL 1), R Pin (CHANNEL 2)

**Simplex Theory Configurations:** Data flow is unidirectional and Point-to-Point from one Driver to one Receiver. NB3N200S device provide a high signal current allowing long drive run and high noise immunity. Single terminated interconnects yield high amplitude levels.

Figure 18. Point-to-Point Simplex Single Termination

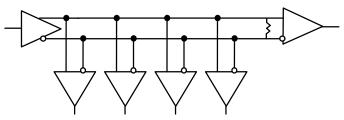

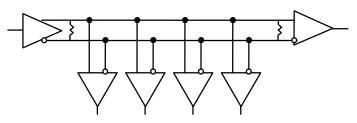

**Simplex Multidrop Theory Configurations**: Data flow is unidirectional from one Driver with one or more Receivers and Multiple boards are required. Single terminated interconnects yield high amplitude levels. Parallel terminated interconnects yield typical MLVDS amplitude Parallel terminated interconnects yield typical MLVDS amplitude levels and minimizes reflections. See Figures 18 and 19. A NB3N200S can be used as the driver or as a receiver.

Figure 19. Parallel–Terminated Simplex

levels and minimizes reflections. On the Evaluation Test Board, Headers P1, P2, and P3 may be used as need to interconnect transceivers to a each other or a bus. See Figures 20 and 21. A NB3N200S can be used as the driver or as a receiver.

Figure 20. Multidrop or Distributed Simplex with Single Termination

Figure 21. Multidrop or Distributed Simplex with Double Termination

Half Duplex Multinode Multipoint Theory Configurations: Data flow is unidirectional and selected from one of multiple possible Drivers to multiple Receives. One "Two Node" multipoint connection can be accomplished with a single evaluation board. More than Two Nodes requires multiple evaluation test boards. Parallel terminated interconnects yield typical MLVDS amplitude levels and minimizes reflections. Parallel terminated interconnects yield typical LMVDS amplitude levels and minimizes reflections. On the Test Board, Headers P1, P2, and P3 may be used as need to interconnect transceivers to each other or a bus. See Figure 22. A NB3N200S can be used as the driver or as a receiver.

Figure 22. Multinode Multipoint Half Duplex (requires Double Termination)

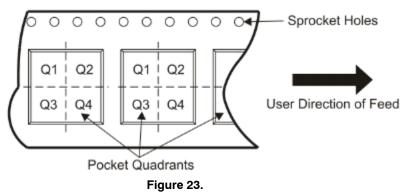

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### **ORDERING INFORMATION**

| Device       | Receiver | Pin 1 Quadrant | Package               | Shipping <sup>†</sup> |

|--------------|----------|----------------|-----------------------|-----------------------|

| NB3N200SDR2G | Type 1   | Q1             | SOIC – 8<br>(Pb–Free) | 2500 / Tape & Reel    |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, <u>BRD8011/D</u>.

# onsemi

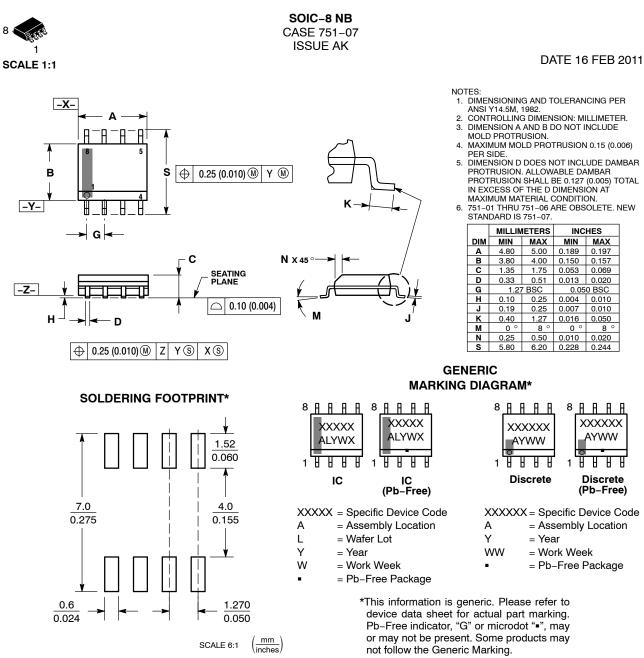

\*For additional information on our Pb-Free strategy and soldering details, please download the **onsemi** Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### STYLES ON PAGE 2

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SOIC-8 NB   |                                                                                                                                                                                     | PAGE 1 OF 2 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |                                                                                                                                                                                     |             |  |

| onsemi and ONSEMI. are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves<br>the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular<br>purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation<br>special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others. |             |                                                                                                                                                                                     |             |  |

#### SOIC-8 NB CASE 751-07 ISSUE AK

STYLE 1: PIN 1. EMITTER COLLECTOR 2. COLLECTOR 3. 4. EMITTER 5. EMITTER BASE 6. 7 BASE EMITTER 8. STYLE 5: PIN 1. DRAIN 2. DRAIN З. DRAIN DRAIN 4. GATE 5. 6. GATE SOURCE 7. 8. SOURCE STYLE 9: PIN 1. EMITTER, COMMON COLLECTOR, DIE #1 COLLECTOR, DIE #2 2. З. EMITTER, COMMON 4. 5. EMITTER, COMMON 6 BASE. DIE #2 BASE, DIE #1 7. 8. EMITTER, COMMON STYLE 13: PIN 1. N.C. 2. SOURCE 3 GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 17: PIN 1. VCC 2. V2OUT V10UT З. TXE 4. 5. RXE 6. VFF 7. GND 8. ACC STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3 CATHODE 3 CATHODE 4 4. 5. CATHODE 5 6. COMMON ANODE COMMON ANODE 7. 8. CATHODE 6 STYLE 25: PIN 1. VIN 2 N/C REXT З. 4. GND 5. IOUT 6. IOUT IOUT 7. 8. IOUT STYLE 29: BASE, DIE #1 PIN 1. 2 EMITTER, #1 BASE, #2 З. EMITTER, #2 4. 5 COLLECTOR, #2 COLLECTOR, #2 6.

STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 COLLECTOR, #2 3. 4 COLLECTOR, #2 BASE, #2 5. EMITTER, #2 6. 7 BASE #1 EMITTER, #1 8. STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN SOURCE 4. SOURCE 5. 6. GATE GATE 7. 8. SOURCE STYLE 10: GROUND PIN 1. BIAS 1 OUTPUT 2. З. GROUND 4. 5. GROUND 6 BIAS 2 INPUT 7. 8. GROUND STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3 P-SOURCE P-GATE 4. P-DRAIN 5 6. P-DRAIN N-DRAIN 7. N-DRAIN 8. STYLE 18: PIN 1. ANODE ANODE 2. SOURCE 3. GATE 4. 5. DRAIN 6 DRAIN CATHODE 7. 8. CATHODE STYLE 22: PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3 COMMON CATHODE/VCC 4. I/O LINE 3 COMMON ANODE/GND 5. 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND STYLE 26: PIN 1. GND 2 dv/dt З. ENABLE 4. ILIMIT 5. SOURCE SOURCE 6. SOURCE 7. 8. VCC STYLE 30: DRAIN 1 PIN 1. DRAIN 1 2 GATE 2 З. SOURCE 2 4. SOURCE 1/DRAIN 2 SOURCE 1/DRAIN 2 5. 6.

STYLE 3: PIN 1. DRAIN, DIE #1 DRAIN, #1 2. DRAIN, #2 З. DRAIN, #2 4. GATE, #2 5. SOURCE, #2 6. 7 GATE #1 8. SOURCE, #1 STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS THIRD STAGE SOURCE GROUND З. 4. 5. DRAIN 6. GATE 3 SECOND STAGE Vd 7. FIRST STAGE Vd 8. STYLE 11: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. DRAIN 2 DRAIN 1 7. 8. DRAIN 1 STYLE 15: PIN 1. ANODE 1 2. ANODE 1 ANODE 1 3 ANODE 1 4. 5. CATHODE, COMMON CATHODE, COMMON CATHODE, COMMON 6. 7. CATHODE, COMMON 8. STYLE 19: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 8. **MIRROR 1** STYLE 23: PIN 1. LINE 1 IN COMMON ANODE/GND COMMON ANODE/GND 2. 3 LINE 2 IN 4. LINE 2 OUT 5. COMMON ANODE/GND COMMON ANODE/GND 6. 7. 8. LINE 1 OUT STYLE 27: PIN 1. ILIMIT 2 OVI 0 UVLO З. 4. INPUT+ 5. 6. SOURCE SOURCE SOURCE 7. 8 DRAIN

#### STYLE 4: PIN 1. 2. ANODE ANODE ANODE З. 4. ANODE ANODE 5. 6. ANODE 7 ANODE COMMON CATHODE 8. STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 BASE #2 З. COLLECTOR, #2 4. COLLECTOR, #2 5. 6. EMITTER, #2 EMITTER, #1 7. 8. COLLECTOR, #1 STYLE 12: PIN 1. SOURCE SOURCE 2. 3. GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 16 EMITTER, DIE #1 PIN 1. 2. BASE, DIE #1 EMITTER, DIE #2 3 BASE, DIE #2 4. 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 COLLECTOR, DIE #1 7. COLLECTOR, DIE #1 8. STYLE 20: PIN 1. SOURCE (N) GATE (N) SOURCE (P) 2. 3. 4. GATE (P) 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 24: PIN 1. BASE EMITTER 2. 3 COLLECTOR/ANODE COLLECTOR/ANODE 4. 5. CATHODE

6. CATHODE COLLECTOR/ANODE 7. 8. COLLECTOR/ANODE STYLE 28: PIN 1. SW\_TO\_GND 2. DASIC OFF DASIC\_SW\_DET З. 4. GND 5. 6. V MON VBULK 7. VBULK

7. VOULK 8. VIN

| DOCUMENT NUMBER: | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                                                                     | PAGE 2 OF 2 |

|                  |             |                                                                                                                                                                                     |             |

SOURCE 1/DRAIN 2

7.

8. GATE 1

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights or others.

7.

8

COLLECTOR, #1

COLLECTOR, #1

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>