# VS-P400 Series

Vishay Semiconductors

### Power Modules, Passivated Assembled Circuit Elements, 40 A

www.vishay.com

PACE-PAK (D-19)

| PRIMARY CHARACTERISTICS |                               |  |  |  |  |

|-------------------------|-------------------------------|--|--|--|--|

| Io                      | 40 A                          |  |  |  |  |

| Туре                    | Modules - thyristor, standard |  |  |  |  |

| Package                 | PACE-PAK (D-19)               |  |  |  |  |

#### FEATURES

- · Glass passivated junctions for greater reliability

- Electrically isolated base plate

- Available up to 1200 V<sub>RRM</sub>/V<sub>DRM</sub>

- High dynamic characteristics

- · Wide choice of circuit configurations

- Simplified mechanical design and assembly

- UL E78996 approved 😱

- Material categorization: for definitions of compliance please see <u>www.vishay.com/doc?99912</u>

#### DESCRIPTION

The VS-P400 series of integrated power circuits consists of power thyristors and power diodes configured in a single package. With its isolating base plate, mechanical designs are greatly simplified giving advantages of cost reduction and reduced size.

Applications include power supplies, control circuits and battery chargers.

| MAJOR RATINGS AND CHARACTERISTICS |                 |             |                  |  |  |  |  |

|-----------------------------------|-----------------|-------------|------------------|--|--|--|--|

| SYMBOL                            | CHARACTERISTICS | VALUES      | UNITS            |  |  |  |  |

| I <sub>O</sub>                    | 80 °C           | 40          | А                |  |  |  |  |

| I <sub>TSM</sub> ,                | 50 Hz           | 385         | А                |  |  |  |  |

| I <sub>FSM</sub>                  | 60 Hz           | 400         | A                |  |  |  |  |

| l <sup>2</sup> t                  | 50 Hz           | 745         | A <sup>2</sup> s |  |  |  |  |

| 1-1                               | 60 Hz           | 680         | A-5              |  |  |  |  |

| l²√t                              |                 | 7450        | A²√s             |  |  |  |  |

| V <sub>RRM</sub>                  | Range           | 400 to 1200 | V                |  |  |  |  |

| V <sub>ISOL</sub>                 |                 | 2500        | V                |  |  |  |  |

| TJ                                |                 | -40 to +125 | °C               |  |  |  |  |

| T <sub>Stg</sub>                  |                 | -40 10 +125 | U                |  |  |  |  |

#### **ELECTRICAL SPECIFICATIONS**

| VOLTAGE RATINGS           |                                                                                                            |                                                                           |                                                             |  |  |  |

|---------------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------|--|--|--|

| TYPE NUMBER               | V <sub>RRM</sub> /V <sub>DRM</sub> , MAXIMUM<br>REPETITIVE PEAK REVERSE AND<br>PEAK OFF-STATE VOLTAGE<br>V | V <sub>RSM</sub> , MAXIMUM<br>NON-REPETITIVE PEAK<br>REVERSE VOLTAGE<br>V | I <sub>RRM</sub> MAXIMUM<br>AT T <sub>J</sub> MAXIMUM<br>mA |  |  |  |

| VS-P401, VS-P421, VS-P431 | 400                                                                                                        | 500                                                                       |                                                             |  |  |  |

| VS-P402, VS-P422, VS-P432 | 600                                                                                                        | 700                                                                       |                                                             |  |  |  |

| VS-P403, VS-P423, VS-P433 | P403, VS-P423, VS-P433 800                                                                                 |                                                                           | 10                                                          |  |  |  |

| VS-P404, VS-P424, VS-P434 | 1000                                                                                                       | 1100                                                                      |                                                             |  |  |  |

| VS-P405, VS-P425, VS-P435 | 1200                                                                                                       | 1300                                                                      |                                                             |  |  |  |

Revision: 27-Jul-2018 1 Document Number: 93755 For technical questions within your region: <u>DiodesAmericas@vishay.com</u>, <u>DiodesAsia@vishay.com</u>, <u>DiodesEurope@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc?91000</u>

COMPLIANT

**Vishay Semiconductors**

| PARAMETER                                                | SYMBOL              | TEST CONDITIONS                                                                                                                                                                |                                  |                                    | VALUES | UNITS            |

|----------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------------------------|--------|------------------|

| Maximum DC output current                                | 1                   | Eull bridge                                                                                                                                                                    | Full bridge circuits             |                                    | 40     | А                |

| at case temperature                                      | I <sub>O</sub>      | Full bridge                                                                                                                                                                    | circuits                         |                                    | 80     | °C               |

|                                                          |                     | t = 10 ms                                                                                                                                                                      | No voltage                       |                                    | 385    |                  |

| Maximum peak, one-cycle                                  | I <sub>TSM</sub> ,  | t = 8.3 ms                                                                                                                                                                     | reapplied                        |                                    | 400    | ^                |

| non-repetitive on-state or<br>forward current            | I <sub>FSM</sub>    | t = 10 ms                                                                                                                                                                      | 100 % V <sub>BBM</sub>           |                                    | 325    | A                |

|                                                          |                     | t = 8.3 ms                                                                                                                                                                     | reapplied                        | Sinusoidal half wave,              | 340    | 1                |

| Maximum I <sup>2</sup> t for fusing                      |                     | t = 10 ms                                                                                                                                                                      | No voltage                       | initial $T_J = T_J$ maximum        | 745    | A <sup>2</sup> s |

|                                                          | l <sup>2</sup> t    | t = 8.3 ms                                                                                                                                                                     | reapplied                        | -                                  | 680    |                  |

|                                                          |                     | t = 10 ms                                                                                                                                                                      | 100 % V <sub>BBM</sub>           |                                    | 530    |                  |

|                                                          |                     | t = 8.3 ms                                                                                                                                                                     | reapplied                        |                                    | 480    |                  |

| Maximum I <sup>2</sup> $\sqrt{t}$ for fusing             | l²√t                | t = 0.1 ms to 10 ms, no voltage reapplied<br>$l^{2}t$ for time tx = $l^{2}\sqrt{t} \cdot \sqrt{tx}$                                                                            |                                  |                                    | 7450   | A²√s             |

| Low level value of threshold voltage                     | V <sub>T(TO)1</sub> | (16.7 % x π                                                                                                                                                                    | : x I <sub>T(AV)</sub> < I < π x | $I_{T(AV)}$ ), $T_J = T_J$ maximum | 0.83   | V                |

| High level value of threshold voltage                    | V <sub>T(TO)2</sub> | $(I > \pi \times I_{T(AV)})$                                                                                                                                                   | ), TJ = TJ maxim                 | num                                | 1.03   | v                |

| Low level value of on-state slope resistance             | r <sub>t1</sub>     | (16.7 % x π                                                                                                                                                                    | x I <sub>T(AV)</sub> < I < π x   | $I_{T(AV)}$ ), $T_J = T_J$ maximum | 9.61   |                  |

| High level value of on-state slope resistance            | r <sub>t2</sub>     | $(I > \pi \times I_{T(AV)}), T_J = T_J \text{ maximum}$                                                                                                                        |                                  | 7.01                               | mΩ     |                  |

| Maximum on-state voltage drop                            | V <sub>TM</sub>     | $I_{TM} = \pi \times I_{T(T)}$                                                                                                                                                 | (AV)                             | T <sub>J</sub> = 25 °C             | 1.4    | V                |

| Maximum forward voltage drop                             | V <sub>FM</sub>     | $I_{FM} = \pi \times I_{F(AV)}$ $T_J = 25 \text{ °C}$                                                                                                                          |                                  | 1.4                                | V      |                  |

| Maximum non-repetitive rate of rise of turned-on current | dl/dt               | $\begin{array}{l} T_{J} = 125 \ ^{\circ}C \ from \ 0.67 \ V_{DRM} \\ I_{TM} = \pi \ x \ I_{T(AV)}, \ I_{g} = 500 \ mA, \ t_{r} < 0.5 \ \mu s, \ t_{p} > 6 \ \mu s \end{array}$ |                                  | 200                                | A/µs   |                  |

| Maximum holding current                                  | Ι <sub>Η</sub>      | т об ос                                                                                                                                                                        |                                  | GV registive lead                  | 130    |                  |

| Maximum latching current                                 | ١L                  | $T_J = 25$ °C anode supply = 6 V, resistive load                                                                                                                               |                                  | 250                                | mA     |                  |

| BLOCKING                                                                                  |                                        |                                                                                              |     |      |  |

|-------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------|-----|------|--|

| PARAMETER                                                                                 | SYMBOL TEST CONDITIONS VALUES          |                                                                                              |     |      |  |

| Maximum critical rate of rise of off-state voltage                                        | dV/dt                                  | $T_{J}$ = 125 °C, exponential to 0.67 $V_{DRM}$ gate open                                    | 200 | V/µs |  |

| Maximum peak reverse and off-state leakage current at V <sub>RRM</sub> , V <sub>DRM</sub> | I <sub>RRM</sub> ,<br>I <sub>DRM</sub> | $I_1 = 125 \text{ G}$ , gate open circuit                                                    |     | mA   |  |

| Maximum peak reverse leakage current                                                      | I <sub>RRM</sub>                       | T <sub>J</sub> = 25 °C                                                                       | 100 | μA   |  |

| RMS isolation voltage                                                                     | V <sub>ISOL</sub>                      | $V_{ISOL}$ 50 Hz, circuit to base, all terminals shorted,<br>T <sub>J</sub> = 25 °C, t = 1 s |     | V    |  |

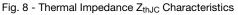

| TRIGGERING                                 |                    |                                                                      |                    |        |       |

|--------------------------------------------|--------------------|----------------------------------------------------------------------|--------------------|--------|-------|

| PARAMETER                                  | SYMBOL             | TEST CO                                                              | NDITIONS           | VALUES | UNITS |

| Maximum peak gate power                    | P <sub>GM</sub>    |                                                                      |                    | 8      | W     |

| Maximum average gate power                 | P <sub>G(AV)</sub> |                                                                      |                    | 2      | vv    |

| Maximum peak gate current                  | I <sub>GM</sub>    |                                                                      |                    | 2      | А     |

| Maximum peak negative gate voltage         | -V <sub>GM</sub>   |                                                                      |                    | 10     | V     |

| Maximum gate voltage required to trigger   | V <sub>GT</sub>    | T <sub>J</sub> = - 40 °C                                             |                    | 3      | V     |

|                                            |                    | T <sub>J</sub> = 25 °C                                               | Anode supply =     | 2      |       |

|                                            |                    | T <sub>J</sub> = 125 °C                                              |                    | 1      |       |

|                                            |                    | T <sub>J</sub> = - 40 °C                                             | 6 V resistive load | 90     |       |

| Maximum gate current required to trigger   | I <sub>GT</sub>    | T <sub>J</sub> = 25 °C                                               |                    | 60     | mA    |

|                                            |                    | T <sub>J</sub> = 125 °C                                              |                    | 35     |       |

| Maximum gate voltage that will not trigger | V <sub>GD</sub>    | $T_J = 125 \text{ °C}, \text{ rated } V_{DRM} \text{ applied}$ $0.2$ |                    | 0.2    | V     |

| Maximum gate current that will not trigger | I <sub>GD</sub>    |                                                                      |                    | 2      | mA    |

Revision: 27-Jul-2018

## **VS-P400 Series**

**Vishay Semiconductors**

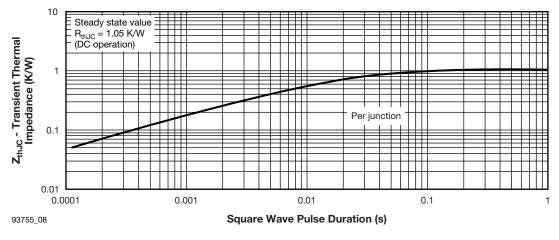

| THERMAL AND MECHANICAL SPECIFICATIONS                       |                                   |                                      |                 |       |

|-------------------------------------------------------------|-----------------------------------|--------------------------------------|-----------------|-------|

| PARAMETER                                                   | SYMBOL                            | TEST CONDITIONS                      | VALUES          | UNITS |

| Maximum junction operating<br>and storage temperature range | T <sub>J</sub> , T <sub>Stg</sub> |                                      | -40 to +125     | °C    |

| Maximum thermal resistance, junction to case per junction   | R <sub>thJC</sub>                 | R <sub>thJC</sub> DC operation       |                 | K/W   |

| Maximum thermal resistance, case to heatsink                | R <sub>thCS</sub>                 | Mounting surface, smooth and greased | 0.10            | r/ w  |

| Mounting torque, base to heatsink <sup>(1)</sup>            |                                   |                                      | 4               | Nm    |

| Approximate weight                                          |                                   |                                      | 58              | g     |

| Approximate weight                                          |                                   |                                      | 2.0             | oz.   |

| Case style                                                  |                                   |                                      | PACE-PAK (D-19) |       |

Note

(1) A mounting compound is recommended and the torque should be checked after a period of 3 hours to allow for the spread of the compound

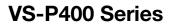

Fig. 1 - Current Ratings Nomogram (1 Module Per Heatsink)

Revision: 27-Jul-2018

3

Document Number: 93755

For technical questions within your region: <u>DiodesAmericas@vishay.com</u>, <u>DiodesAsia@vishay.com</u>, <u>DiodesEurope@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc?91000</u>

### **Vishay Semiconductors**

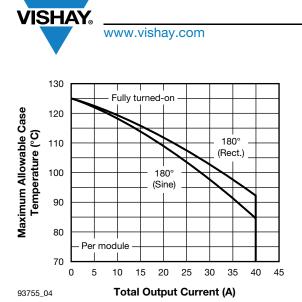

Fig. 4 - Current Ratings Characteristics

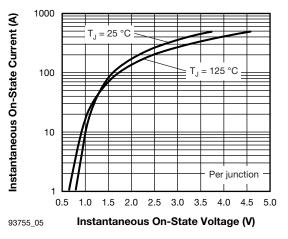

Fig. 5 - On-State Voltage Drop Characteristics

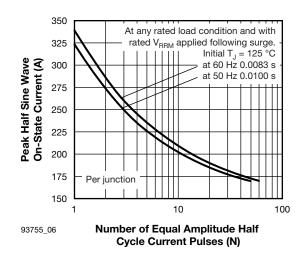

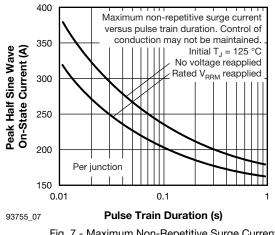

Fig. 6 - Maximum Non-Repetitive Surge Current

Revision: 27-Jul-2018 Document Number: 93755 4 For technical questions within your region: DiodesAmericas@vishay.com, DiodesAsia@vishay.com, DiodesEurope@vishay.com THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishav.com/doc?91000

Fig. 9 - Gate Characteristics

### **ORDERING INFORMATION TABLE**

| Device code | VS-         | Р                    | 4                                                                                                                                                                       | 0         | 2       | к      | w |  |

|-------------|-------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|--------|---|--|

|             | 1           | 2                    | 3                                                                                                                                                                       | 4         | 5       | 6      | 7 |  |

|             | 1<br>2<br>3 | - M<br>- C<br>1<br>4 | Vishay Semiconductors product<br>Module type<br>Current rating<br>1 = 25 A DC (P100 series)<br>4 = 40 A DC (P400 series)<br>Circuit configuration                       |           |         |        |   |  |

|             |             | 0<br>2               | <ul> <li>0 = single phase, hybrid bridge common cathode</li> <li>2 = single phase, hybrid bridge doubler connectio</li> <li>3 = single phase, all SCR bridge</li> </ul> |           |         |        |   |  |

|             | 5           | 1<br>2<br>3<br>4     | bltage cod<br>= 400 V<br>= 600 V<br>= 800 V<br>= 1000 V<br>= 1200 V                                                                                                     |           |         |        |   |  |

|             | 6           | - K                  | = optiona                                                                                                                                                               | al voltag | e suppr | ession |   |  |

|             | 7           | - W                  | = option                                                                                                                                                                | al freew  | heeling | diode  |   |  |

www.vishay.com

### Vishay Semiconductors

| CIRCUIT CONFIGURATION                             |                                  |                                                              |                                                        |  |

|---------------------------------------------------|----------------------------------|--------------------------------------------------------------|--------------------------------------------------------|--|

| CIRCUIT DESCRIPTION                               | CIRCUIT<br>CONFIGURATION<br>CODE | SCHEMATIC DIAGRAM                                            | TERMINAL POSITIONS                                     |  |

| Single phase, hybrid bridge<br>common cathode     | 0                                | (-) $(-)$ $(+)$ $(+)$ $(+)$                                  | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ |  |

| Single phase, hybrid bridge<br>doubler connection | 2                                | $G1 \circ G2$<br>$AC2 \circ AC1 \circ O$<br>$(-) \circ O(+)$ | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ |  |

| Single phase, all SCR bridge                      | 3                                | $G^{3}$ $G^{3}$ $G^{1}$ $AC_{2}$ $G^{4}$ $G^{2}$ $(+)$       | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ |  |

| CODING <sup>(1)</sup>                          |                                  |                 |                             |                               |                                                               |  |  |

|------------------------------------------------|----------------------------------|-----------------|-----------------------------|-------------------------------|---------------------------------------------------------------|--|--|

| CIRCUIT DESCRIPTION                            | CIRCUIT<br>CONFIGURATION<br>CODE | BASIC<br>SERIES | WITH VOLTAGE<br>SUPPRESSION | WITH<br>FREEWHEELING<br>DIODE | WITH BOTH<br>VOLTAGE SUPPRESSION<br>AND FREEWHEELING<br>DIODE |  |  |

| Single phase, hybrid bridge common cathode     | 0                                | P40.            | P40.K                       | P40.W                         | P40.KW                                                        |  |  |

| Single phase, hybrid bridge doubler connection | 2                                | P42.            | P42.K                       | -                             | -                                                             |  |  |

| Single phase, all SCR bridge                   | 3                                | P43.            | P43.K                       | -                             | -                                                             |  |  |

#### Note

<sup>(1)</sup> To complete code refer to Voltage Ratings table, i.e.: for 600 V P40.W complete code is P402W

| LINKS TO RELATED DOCUMENTS |                          |  |  |  |

|----------------------------|--------------------------|--|--|--|

| Dimensions                 | www.vishay.com/doc?95335 |  |  |  |

Vishay Semiconductors

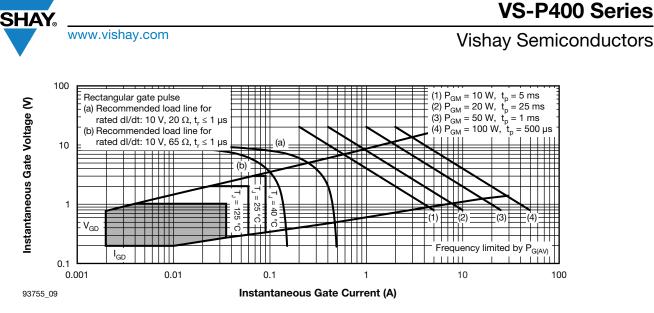

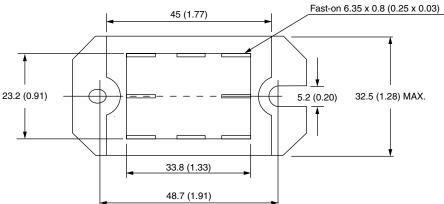

# **D-19 PACE-PAK**

### **DIMENSIONS** in millimeters (inches)

SHAY

Vishay

### Disclaimer

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Hyperlinks included in this datasheet may direct users to third-party websites. These links are provided as a convenience and for informational purposes only. Inclusion of these hyperlinks does not constitute an endorsement or an approval by Vishay of any of the products, services or opinions of the corporation, organization or individual associated with the third-party website. Vishay disclaims any and all liability and bears no responsibility for the accuracy, legality or content of the third-party website or for that of subsequent links.

Vishay products are not designed for use in life-saving or life-sustaining applications or any application in which the failure of the Vishay product could result in personal injury or death unless specifically qualified in writing by Vishay. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

© 2024 VISHAY INTERTECHNOLOGY, INC. ALL RIGHTS RESERVED

Revision: 01-Jul-2024