End of Life, Last Available Purchase Date is 31-Dec-2014

### SiP21106, SiP21107, SiP21108

**Vishay Siliconix**

# 150-mA Low Noise, Low Dropout Regulator

#### DESCRIPTION

The SiP21106 BiCMOS 150 mA low noise LDO voltage regulators are the perfect choice for low battery operated low powered applications. An ultra low ground current and low dropout voltage of 135 mV at 150 mA load helps to extend battery life for portable electronics. Systems requiring a quiet voltage source, such as RF applications, will benefit from the SiP21106 low output noise.

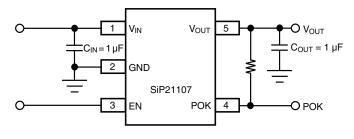

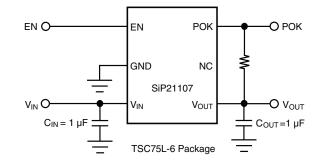

The SiP21107 do not require a noise bypass capacitor and provides an error flag pin (POK or Power OK). POK output requires an external pull-up resistor and goes low when the supply has not come up to voltage.

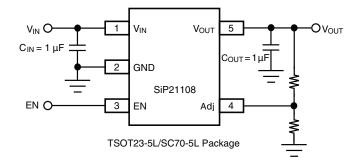

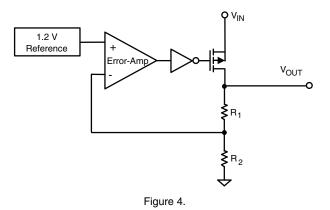

The SiP21108 output is adjusted with an external resistor network.

The SiP21106, SiP21107, SiP21108 regulators allow stable operation with very small ceramic output capacitors, reducing board space and component cost. They are designed to maintain regulation while delivering 330 mA peak current upon turn-on. During start-up, an active pull-down circuit improves the output transient response and regulation. In shutdown mode, the output automatically discharges to ground through a 100  $\Omega$  NMOS.

The SiP21106, SiP21107, SiP21108 are available in TSOT23-5L a super thin lead (Pb)-free TSC75-6L and SC70-5L packages for operation over the industrial operation range (- 40 °C to 85 °C).

### **FEATURES**

- SC70-5L (2.1 mm x 2.1 mm x 0.95 mm)

- TSOT23-5L (3.05 mm x 2.85 mm x 1.0 mm)

RoHS

COMPLIANT

- TSC75-6L package (1.6 mm x 1.6 mm x 0.55 mm), TSOT23-5L and SC70-5L Package Options

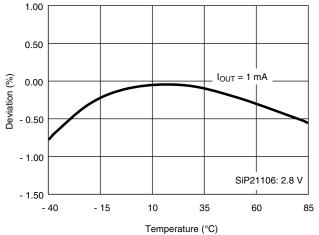

- 1.0 % output voltage accuracy at 25 °C

- Low dropout voltage: 135 mV at 150 mA •

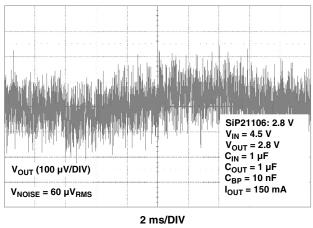

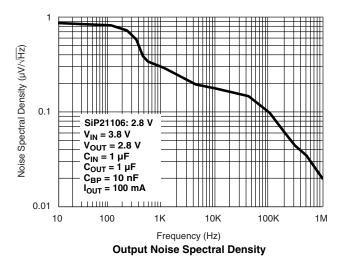

- SiP21106 low noise: 60  $\mu V_{(rms)}$  (10 Hz to 100 kHz bandwidth) with 10 nF over full load range

- 35 µA (typical) ground current at 1 mA load

- 1 µA maximum shutdown current at 85 °C

- Output auto discharge at shutdown mode

- Built-in short circuit (330 mA typical) and thermal protection (160 °C typical)

- SiP21108 adjustable output voltage

- SiP21107 POK Error Flag

- 40 °C to + 125 °C junction temperature range for operation

- Uses low ESR ceramic capacitors

- Fixed voltage output 1.2 V to 5 V in 50 mV steps

- Compliant to RoHS Directive 2002/95/EC

#### **APPLICATIONS**

- Cellular phones, wireless handsets

- PDAs

- MP3 players

- **Digital cameras**

- Pagers

- Wireless modem

- Noise-sensitive electronic systems

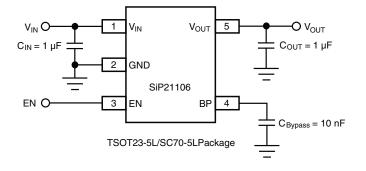

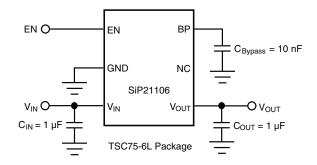

**TYPICAL APPLICATION CIRCUIT**

Vishay Siliconix

### TYPICAL APPLICATION CIRCUIT

TSOT23-5L/SC70-5LPackage

| ABSOLUTE MAXIMUM RATINGS                                 |          |                                |         |      |  |  |

|----------------------------------------------------------|----------|--------------------------------|---------|------|--|--|

| Parameter                                                |          | Limit                          |         | Unit |  |  |

| Input Voltage, V <sub>IN</sub> to GND                    |          | - 0.3 to 6.5                   |         | V    |  |  |

| V <sub>EN</sub> (See Detailed Description)               |          | - 0.3 to 6.5                   |         |      |  |  |

| Output Current (I <sub>OUT</sub> )                       | S        | Short Circuit Protected        |         |      |  |  |

| Output Voltage (V <sub>OUT</sub> )                       |          | - 0.3 to V <sub>IN</sub> + 0.3 |         |      |  |  |

|                                                          | TSC75-6L | TSOT23-5L                      | SC70-5L |      |  |  |

| Package Power Dissipation (P <sub>D</sub> ) <sup>a</sup> | 420      | 305                            | 187     | mW   |  |  |

| Package Thermal Resistance $(\theta_{JA})^{b}$           | 131      | 180                            | 294     | °C/W |  |  |

| Maximum Junction Temperature, $T_{J(max)}$               |          | 125                            |         |      |  |  |

| Storage Temperature, T <sub>STG</sub>                    |          | - 65 to 150                    |         |      |  |  |

| Lead Temperature, TL <sup>c</sup>                        |          | 260                            |         |      |  |  |

Notes:

a. Derate 7.6 mW/°C for TSC75-6L package, 5.5 mW/°C for TSOT23-5L and 3.4 mW/°C for SC70-5L package above  $T_A = 70$  °C.

b. Device mounted with all leads soldered or welded to multilayer 1S2P PC board.

c. Soldering for 5 s.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating/conditions for extended periods may affect device reliability.

| RECOMMENDED OPERATING RANGE                  |            |      |  |  |  |  |

|----------------------------------------------|------------|------|--|--|--|--|

| Parameter                                    | Limit      | Unit |  |  |  |  |

| Input Voltage, V <sub>IN</sub>               | 2.2 to 6   | V    |  |  |  |  |

| Operating Ambient Temperature T <sub>A</sub> | - 40 to 85 | О°   |  |  |  |  |

# SiP21106, SiP21107, SiP21108 Vishay Siliconix

| SPECIFICATIONS                                            |                                      | Test Conditions Unles                                                                                    | s Specified                   | 1                  | 1                 |                   | Γ                 |     |

|-----------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------|--------------------|-------------------|-------------------|-------------------|-----|

|                                                           |                                      | $V_{IN} = V_{OUT(nom)} + 1.0$                                                                            |                               |                    |                   |                   |                   |     |

|                                                           |                                      | $I_{OUT} = 1 \text{ mA}, C_{IN} = 1 \mu\text{F},$                                                        |                               |                    |                   |                   |                   |     |

| Devementer                                                | Symbol                               | - 40 °C < T <sub>A</sub> < 85 °(                                                                         |                               | Tama a             | Min. <sup>b</sup> | Typ. <sup>c</sup> | Max. <sup>b</sup> | 11  |

| Parameter                                                 | Symbol                               | -40 C < 1A < 65 (                                                                                        |                               | Temp. <sup>a</sup> |                   | Typ.*             | 1                 |     |

| Input Voltage Range                                       | V <sub>IN</sub>                      |                                                                                                          |                               | Full               | 2.2               |                   | 6                 | V   |

|                                                           |                                      | I <sub>OUT</sub> = 1 mA                                                                                  | N N                           | Room               | - 1.0             |                   | 1.0               |     |

| Output Voltage Accuracy                                   | V <sub>OUT</sub>                     |                                                                                                          |                               | Full               | - 2.5             |                   | 2.5               | %   |

|                                                           | -001                                 | SiP21106/7 (1.2 V) I <sub>O</sub>                                                                        | uт = 1 mA                     | Room               | - 1.5             |                   | 1.5               | ,-  |

|                                                           |                                      |                                                                                                          | 01                            | Full               | - 4               |                   | 4                 |     |

| Feedback Voltage                                          | V                                    |                                                                                                          |                               | Room               | 1.188             | 1.2               | 1.212             | v   |

| (SiP21108 Version only)                                   | V <sub>Adj</sub>                     |                                                                                                          |                               | Full               | 1.170             |                   | 1.230             | ľ   |

| Line Regulation                                           | LNR                                  |                                                                                                          |                               | Full               | - 0.2             | 0.006             | 0.2               | %/  |

| č                                                         |                                      | V <sub>OUT</sub> ≥ 2.6 V                                                                                 | <u>.</u>                      | _                  |                   |                   |                   |     |

| Lead Devide the                                           | 100                                  | I <sub>OUT</sub> : 1 mA to 15                                                                            | 0 mA                          | Room               |                   | 0.003             | 0.006             |     |

| Load Regulation                                           | LDR                                  | V <sub>OUT</sub> < 2.6 V                                                                                 |                               | D                  |                   | 0.005             | 0.000             | %/n |

|                                                           |                                      | I <sub>OUT</sub> : 1 mA to 15                                                                            |                               | Room               |                   | 0.005             | 0.009             |     |

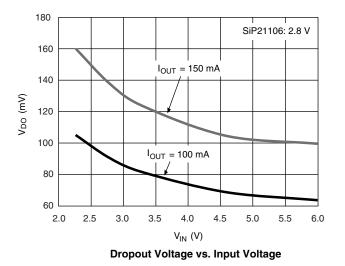

|                                                           |                                      | 1 d                                                                                                      |                               | Room               |                   | 35                | 75                |     |

|                                                           |                                      | I <sub>OUT</sub> = 1 mA                                                                                  |                               | Full               |                   |                   | 85                | İ., |

| Ground Pin Current <sup>e</sup>                           | IGND                                 |                                                                                                          |                               | Room               |                   | 39                | 75                | μA  |

|                                                           |                                      | l <sub>OUT</sub> = 150 mA                                                                                |                               | Full               |                   |                   | 85                | 1   |

| Shutdown Supply Current                                   | 100/10                               | V <sub>EN</sub> = 0 V                                                                                    |                               | Full               |                   | 0.02              | 1                 | μ/  |

| Shataown Supply Sunon                                     | I <sub>CC(off)</sub>                 | SiP21106                                                                                                 |                               | i an               |                   | 0.02              |                   | μ/  |

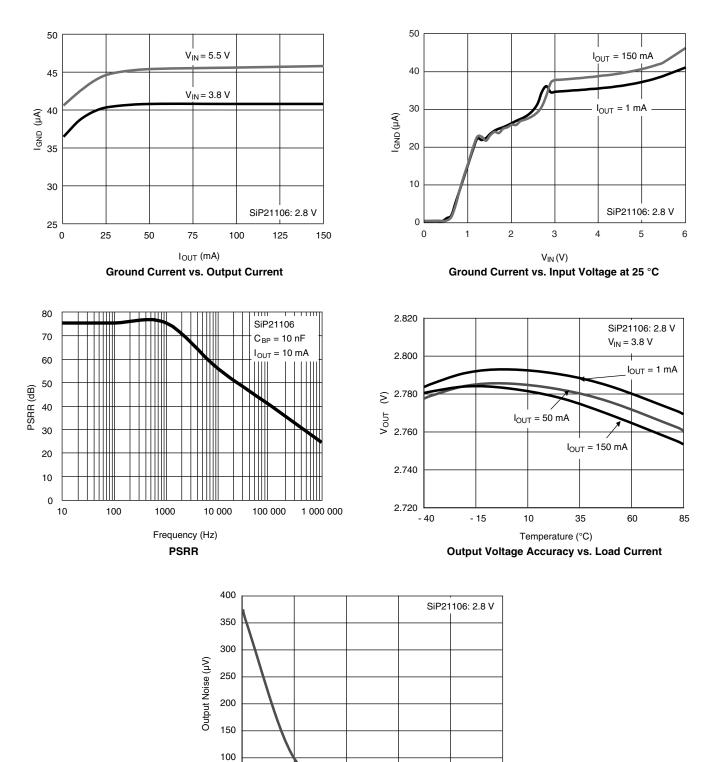

|                                                           |                                      |                                                                                                          | 2.8 V, BW = 10 Hz to 100 kHz, |                    |                   | 60                |                   |     |

| Output Noise Voltage <sup>f</sup> (RMS)                   |                                      | $1 \text{ mA} < I_{OUT} < 150 \text{ mA}, C$                                                             |                               | Room               |                   | 00                |                   | μV  |

|                                                           | e <sub>N</sub>                       | SiP21107/8                                                                                               |                               |                    |                   |                   |                   |     |

|                                                           |                                      | $V_{OUT(nom)} = 2.8 \text{ V}, BW = 10$                                                                  |                               | Room               |                   | 350               |                   |     |

|                                                           |                                      | $1 \text{ mA} < I_{OUT} < 15$                                                                            | 0 mA                          | noom               |                   | 000               |                   |     |

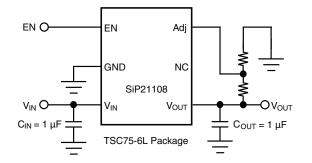

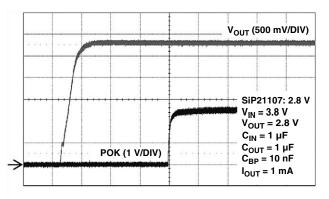

| Output Voltage Turn-On Time                               | t <sub>on</sub>                      | EN to V <sub>OUT</sub> delay; I <sub>OU</sub>                                                            |                               |                    |                   | 70                |                   | μ   |

|                                                           | fon                                  |                                                                                                          | f = 1  kHz                    | Room               |                   | 75                |                   | μ.  |

|                                                           |                                      | SiP21106, $C_{BP} = 0.01 \ \mu F$<br>$I_{OUT} = 10 \ mA$<br>SiP21107/8<br>SiP21106, $C_{BP} = 0 \ \mu F$ | f = 10  kHz                   |                    |                   |                   |                   | dB  |

|                                                           | PSRR                                 |                                                                                                          | -                             | Room               |                   | 56                |                   |     |

| Ripple Rejection                                          |                                      |                                                                                                          | f = 100 kHz                   | Room               |                   | 40                |                   |     |

|                                                           |                                      |                                                                                                          | f = 1 kHz                     | Room               |                   | 72                |                   |     |

|                                                           |                                      |                                                                                                          | f = 10 kHz                    | Room               |                   | 53                |                   |     |

|                                                           |                                      | l <sub>OUT</sub> = 10 mA                                                                                 | f = 100 kHz                   | Room               |                   | 38                |                   |     |

| Output Current Limit                                      | I <sub>O_LIM</sub>                   | V <sub>OUT</sub> = 0 V                                                                                   |                               | Room               | 170               | 330               | 600               | m   |

| Auto Disabarga Desistanas                                 | Б                                    | EN = 0 V, V <sub>OUT</sub> =                                                                             | = 1 V                         | Room               |                   | 100               |                   |     |

| Auto Discharge Resistance                                 | R <sub>DIS</sub>                     | For V <sub>OUT</sub> < 2.2 V, EN = 0                                                                     | V, V <sub>OUT</sub> = 1 V     | Room               |                   | 120               |                   | Ω   |

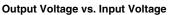

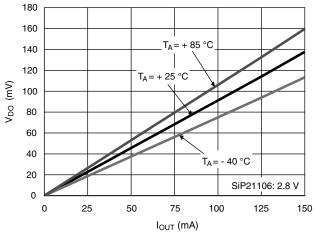

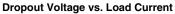

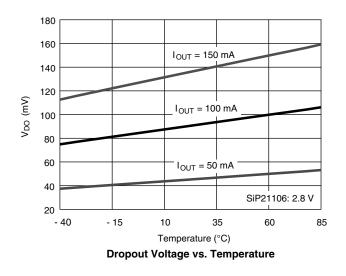

|                                                           |                                      |                                                                                                          |                               | Room               |                   | 45                |                   |     |

|                                                           |                                      | l <sub>OUT</sub> = 50 m/                                                                                 | 4                             | Full               |                   | 55                |                   |     |

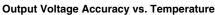

| Dropout Voltage <sup>d</sup>                              |                                      |                                                                                                          |                               | Room               |                   | 90                |                   | 1   |

| $(2.2 \text{ V} \le \text{V}_{OUT(nom)} < 2.6 \text{ V})$ | V <sub>DO</sub>                      | l <sub>OUT</sub> = 100 m                                                                                 | A                             | Full               |                   | 106               |                   | mV  |

|                                                           |                                      |                                                                                                          |                               | Room               |                   | 135               | 250               |     |

|                                                           |                                      | l <sub>OUT</sub> = 150 m                                                                                 | A                             | Full               |                   |                   |                   |     |

|                                                           |                                      |                                                                                                          |                               |                    |                   | 160               | 300               |     |

|                                                           |                                      | I <sub>OUT</sub> = 50 m/                                                                                 | 4                             | Room               |                   | 45                |                   |     |

|                                                           |                                      |                                                                                                          |                               | Full               |                   | 55                |                   |     |

| Dropout Voltage                                           | V <sub>DO</sub>                      | I <sub>OUT</sub> = 100 m                                                                                 | A                             | Room               |                   | 90                |                   |     |

| $(V_{OUT(nom)} \ge 2.6 V)$                                | - 00                                 | .001 = 100 m                                                                                             |                               | Full               |                   | 106               |                   |     |

|                                                           |                                      | l <sub>OUT</sub> = 150 m                                                                                 | Δ                             | Room               |                   | 135               | 180               |     |

|                                                           |                                      | 100T = 150 M                                                                                             | ~                             | Full               |                   | 160               | 220               |     |

|                                                           |                                      |                                                                                                          |                               |                    | 10                |                   | 1                 | 1   |

|                                                           | VENH                                 | High = Regulator On                                                                                      | (Rising)                      | Full               | 1.2               |                   |                   |     |

| EN Pin Input Voltage                                      | V <sub>ENH</sub><br>V <sub>ENL</sub> | High = Regulator On<br>Low = Regulator Off                                                               |                               | Full               | 1.2               |                   | 0.4               | V   |

### Vishay Siliconix

| SPECIFICATIONS                            |                      |                                                                                                                                                                                                                                                   |                    |                   |                   |                   |      |  |  |

|-------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------|-------------------|-------------------|------|--|--|

| Parameter                                 | Symbol               | $\label{eq:VIN} \begin{array}{l} \mbox{Test Conditions Unless Specified} \\ V_{IN} = V_{OUT(nom)} + 1.0 \ V \\ I_{OUT} = 1 \ mA, \ C_{IN} = 1 \ \mu F, \ C_{OUT} = 1 \ \mu F \\ - 40 \ ^{\circ}C < T_A < 85 \ ^{\circ}C \ for \ full \end{array}$ | Temp. <sup>a</sup> | Min. <sup>b</sup> | Typ. <sup>c</sup> | Max. <sup>b</sup> | Unit |  |  |

| Thermal Shutdown Junction Temperature     | T <sub>J(S/D)</sub>  |                                                                                                                                                                                                                                                   | Room               |                   | 160               |                   | °C   |  |  |

| Thermal Hysteresis                        | T <sub>HYST</sub>    |                                                                                                                                                                                                                                                   | Room               |                   | 20                |                   | -0   |  |  |

| Error Flag Section (SiP21107 Version only | y)                   |                                                                                                                                                                                                                                                   | -                  | •                 | •                 |                   |      |  |  |

| POK(OFF) Leakage                          | I <sub>OFF</sub>     | R <sub>PU</sub> to V <sub>OUT</sub> or V <sub>IN</sub>                                                                                                                                                                                            | Full               |                   |                   | 1                 | μA   |  |  |

| POK(ON) Voltage                           | V <sub>POKL</sub>    | EN = 0 V, I <sub>POK</sub> = 0.5 mA                                                                                                                                                                                                               | Full               |                   |                   | 0.4               | V    |  |  |

| POK Threshold <sup>0</sup>                | V                    | $V_{OUT}$ rising, POK goes high $V_{OUT(nom)} \ge 2.2$ V, $I_{OUT} = 1$ mA                                                                                                                                                                        | Eull               | 90                | 93                | 96                |      |  |  |

| POK Threshold <sup>g</sup>                | V <sub>POKLH</sub>   | V <sub>OUT</sub> rising, POK goes high<br>V <sub>OUT(nom)</sub> < 2.2 V, I <sub>OUT</sub> = 1 mA                                                                                                                                                  | - Full             |                   | 91                |                   | %    |  |  |

| POK Hysteresis                            | V <sub>HYST</sub>    | V <sub>IN</sub> falling, I <sub>OUT</sub> = 1 mA, POK goes low                                                                                                                                                                                    | Room               |                   | 1.5               |                   |      |  |  |

| POK Voltage Delay Time                    | T <sub>P_Delay</sub> | V <sub>OUT</sub> to POK delay, I <sub>OUT</sub> = 1 mA                                                                                                                                                                                            |                    |                   | 40                |                   | μs   |  |  |

Notes:

a. Room = 25 °C, Full = - 40 to 85 °C. Derate 7.6 mW/°C for TSC75 and 5.5 mW/°C for SOT23 above  $T_A = 70$  °C.

b. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum.

c. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

d. Dropout voltage is defined as the input-to-output differential voltage at which the output voltage drops 2 % below its nominal value with constant load. For outputs = 2.2 V, dropout voltage is not applicable due to 2.2 V minimum input voltage requirement.

e. Ground current is specified for normal operation as well as "drop-out" operation.

f. Output noise is proportional to output voltage. Use formula  $e_N = 60 \ \mu V (rms)^* V_{OUT}/2.8 \ V.$

g. POK threshold percentage is calculated by V<sub>IN</sub>/V<sub>OUT</sub> x 100 %. The POK is measured with a differential voltage across V<sub>IN</sub> and V<sub>OUT</sub> until POK turn on (low threshold) or off (high threshold). For V<sub>OUT</sub> less than 2.2 V, POK is guaranteed functionality only.

### TIMING WAVEFORMS

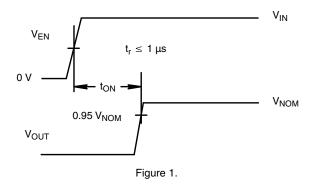

| PIN DESC               | PIN DESCRIPTION                     |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|------------------------|-------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Number<br>TSC75-6L | Pin Number<br>TSOT23-5L/<br>SC70-5L | Name             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 1                      | 3                                   | EN               | By applying less than 0.4 V to this pin, the device will be turned off. Connect this pin to $V_{\rm IN}$ if unused. Do not leave floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 2                      | 2                                   | GND              | Ground pin. For better thermal capability, directly connected to large ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 3                      | 1                                   | V <sub>IN</sub>  | Input supply pin. Bypass this pin with a 1 $\mu\text{F}$ ceramic or tantalum capacitor to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 4                      | 5                                   | V <sub>OUT</sub> | Output voltage. Connect C <sub>OUT</sub> between this pin and ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 5                      | -                                   | NC               | No Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

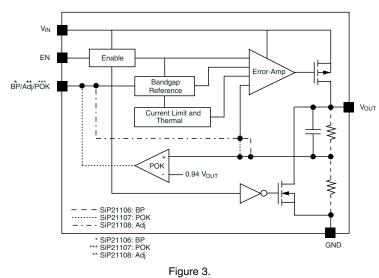

| 6                      | 4                                   | BP/Adj/POK       | <ul> <li>BP (SiP21106): Noise bypass pin. For low noise applications, a 10 nF ceramic capacitor should be connected from this pin to ground.</li> <li>Adj (SiP21108): Adjust input pin. Connect feedback resistors to program the output voltage for trim value of 1.2005 V.</li> <li>POK (SiP21107): Power OK (error flag) pin. Open-drain output, which requires connecting a pull-up resistor to V<sub>IN</sub> or V<sub>OUT</sub>. POK pin is actively high to indicate an output normal operation condition on regulator and goes low to indicate under-voltage fault condition.</li> </ul> |  |  |  |  |

### End of Life. Last Available Purchase Date is 31-Dec-2014

# SiP21106, SiP21107, SiP21108

# Vishay Siliconix

| ORDERING INFORMATION |         |            |                   |           |  |  |  |  |

|----------------------|---------|------------|-------------------|-----------|--|--|--|--|

| Part Number          | Marking | Voltage    | Temperature Range | Package   |  |  |  |  |

| SiP21108DVP-T1-E3    | AA      | Adjustable |                   |           |  |  |  |  |

| SiP21106DVP-12-E3    | BA      | 1.2        |                   |           |  |  |  |  |

| SiP21106DVP-18-E3    | BG      | 1.8        |                   |           |  |  |  |  |

| SiP21106DVP-25-E3    | BP      | 2.5        |                   |           |  |  |  |  |

| SiP21106DVP-26-E3    | BR      | 2.6        |                   |           |  |  |  |  |

| SiP21106DVP-28-E3    | BT      | 2.8        |                   |           |  |  |  |  |

| SiP21106DVP-285-E3   | СТ      | 2.85       |                   |           |  |  |  |  |

| SiP21106DVP-30-E3    | BV      | 3          |                   |           |  |  |  |  |

| SiP21106DVP-33-E3    | BY      | 3.3        |                   |           |  |  |  |  |

| SiP21106DVP-46-E3    | СМ      | 4.6        | - 40 °C to 85 °C  | TSC75-6L  |  |  |  |  |

| SiP21106DVP-475-E3   | CU      | 4.75       | - 40 °C 10 85 °C  | 13075-0L  |  |  |  |  |

| SiP21107DVP-12-E3    | DA      | 1.2        |                   |           |  |  |  |  |

| SiP21107DVP-18-E3    | DG      | 1.8        |                   |           |  |  |  |  |

| SiP21107DVP-25-E3    | DP      | 2.5        |                   |           |  |  |  |  |

| SiP21107DVP-26-E3    | DR      | 2.6        |                   |           |  |  |  |  |

| SiP21107DVP-28-E3    | DT      | 2.8        |                   |           |  |  |  |  |

| SiP21107DVP-30-E3    | DV      | 3          |                   |           |  |  |  |  |

| SiP21107DVP-33-E3    | DY      | 3.3        |                   |           |  |  |  |  |

| SiP21107DVP-46-E3    | EM      | 4.6        |                   |           |  |  |  |  |

| SiP21107DVP-285-E3   | ET      | 2.85       |                   |           |  |  |  |  |

| SiP21108DT-T1-E3     | N9      | Adjustable |                   |           |  |  |  |  |

| SiP21106DT-12-E3     | NP      | 1.2        |                   |           |  |  |  |  |

| SiP21106DT-18-E3     | N1      | 1.8        |                   |           |  |  |  |  |

| SiP21106DT-25-E3     | NA      | 2.5        |                   |           |  |  |  |  |

| SiP21106DT-26-E3     | NC      | 2.6        |                   |           |  |  |  |  |

| SiP21106DT-28-E3     | N2      | 2.8        |                   |           |  |  |  |  |

| SiP21106DT-285-E3    | NE      | 2.85       |                   |           |  |  |  |  |

| SiP21106DT-30-E3     | NG      | 3          |                   |           |  |  |  |  |

| SiP21106DT-33-E3     | N3      | 3.3        |                   |           |  |  |  |  |

| SiP21106DT-45-E3     | NM      | 4.5        |                   |           |  |  |  |  |

| SiP21106DT-46-E3     | N4      | 4.6        | - 40 °C to 85 °C  | TSOT23-5L |  |  |  |  |

| SiP21106DT-475-E3    | NJ      | 4.75       |                   |           |  |  |  |  |

| SiP21107DT-12-E3     | NQ      | 1.2        |                   |           |  |  |  |  |

| SiP21107DT-18-E3     | N5      | 1.8        |                   |           |  |  |  |  |

| SiP21107DT-25-E3     | NB      | 2.5        |                   |           |  |  |  |  |

| SiP21107DT-26-E3     | ND      | 2.6        |                   |           |  |  |  |  |

| SiP21107DT-28-E3     | N6      | 2.8        |                   |           |  |  |  |  |

| SiP21107DT-285-E3    | NF      | 2.85       |                   |           |  |  |  |  |

| SiP21107DT-30-E3     | NH      | 3          |                   |           |  |  |  |  |

| SiP21107DT-33-E3     | N7      | 3.3        |                   |           |  |  |  |  |

| SiP21107DT-46-E3     | N8      | 4.6        |                   |           |  |  |  |  |

### End of Life. Last Available Purchase Date is 31-Dec-2014

## SiP21106, SiP21107, SiP21108

Vishay Siliconix

| ORDERING INFORMAT | ION |            |                  |         |

|-------------------|-----|------------|------------------|---------|

| SiP21108DR-T1-E3  | N9  | Adjustable |                  |         |

| SiP21106DR-12-E3  | NP  | 1.2        |                  |         |

| SiP21106DR-18-E3  | N1  | 1.8        |                  |         |

| SiP21106DR-25-E3  | NA  | 2.5        |                  |         |

| SiP21106DR-26-E3  | NC  | 2.6        |                  |         |

| SiP21106DR-28-E3  | N2  | 2.8        |                  |         |

| SiP21106DR-285-E3 | NE  | 2.85       |                  |         |

| SiP21106DR-30-E3  | NG  | 3          |                  |         |

| SiP21106DR-33-E3  | N3  | 3.3        |                  |         |

| SiP21106DR-46-E3  | N4  | 4.6        | - 40 °C to 85 °C | SC70-5L |

| SiP21106DR-475-E3 | NJ  | 4.75       | - 40 °C 10 85 °C | 5070-5L |

| SiP21107DR-12-E3  | NQ  | 1.2        |                  |         |

| SiP21107DR-18-E3  | N5  | 1.8        |                  |         |

| SiP21107DR-25-E3  | NB  | 2.5        |                  |         |

| SiP21107DR-26-E3  | ND  | 2.6        |                  |         |

| SiP21107DR-28-E3  | N6  | 2.8        |                  |         |

| SiP21107DR-285-E3 | NF  | 2.85       |                  |         |

| SiP21107DR-30-E3  | NH  | 3          | ]                |         |

| SiP21107DR-33-E3  | N7  | 3.3        |                  |         |

| SiP21107DR-46-E3  | N8  | 4.6        |                  |         |

Note:

Other fixed output voltage options are available. Please contact your Vishay sales representative or distributor for details.

**Vishay Siliconix**

### **TYPICAL CHARACTERISTICS**

### End of Life. Last Available Purchase Date is 31-Dec-2014

### SiP21106, SiP21107, SiP21108

**Vishay Siliconix**

### **TYPICAL CHARACTERISTICS**

50 L 0

0.001

0.0056

0.01

BP Capacitance (µF) Output Noise vs. BP Capacitance

0.056

0.1

Vishay Siliconix

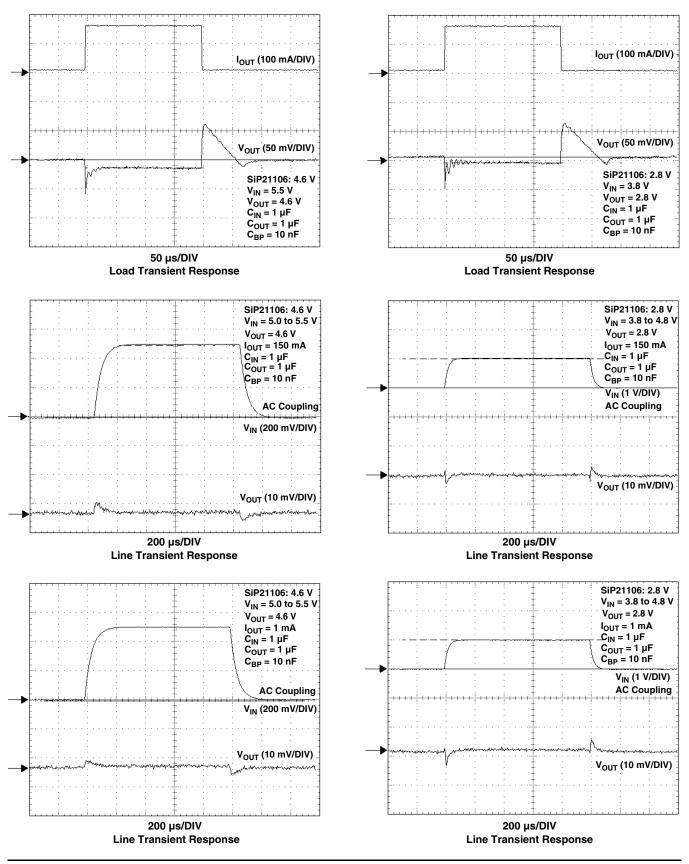

### **TYPICAL OPERATING WAVEFORMS**

### End of Life. Last Available Purchase Date is 31-Dec-2014 SiP21106, SiP21107, SiP21108

**Vishay Siliconix**

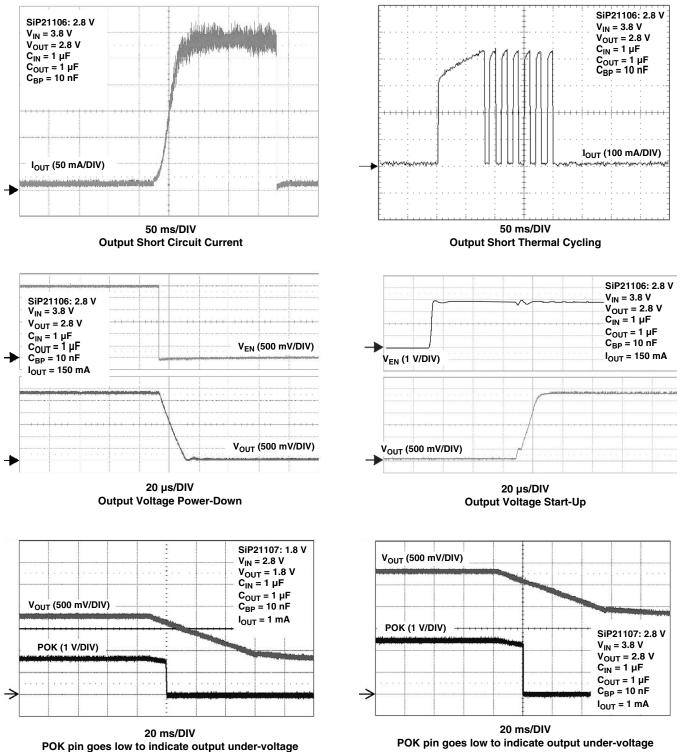

### **TYPICAL OPERATING WAVEFORMS**

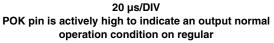

fault condition

fault condition

**Vishay Siliconix**

### **TYPICAL OPERATING WAVEFORMS**

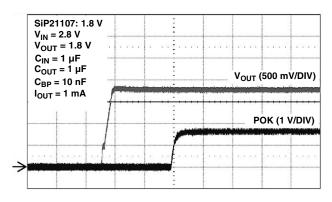

### TYPICAL WAVEFORMS

Output Noise

20 μs/DIV POK pin is actively high to indicate an output normal operation condition on regular

# Vishay Siliconix

#### **DETAILED DESCRIPTION**

As shown in the block diagram, the circuit consists of a bandgap reference, error amplifier, P-channel pass transistor and an internal feedback resistor voltage divider, which is used to monitor and control the output voltage.

A constant 1.2 V bandgap reference voltage is applied to the non-inverting input of the error amplifier. The error amplifier compares this reference with the feedback voltage on its inverting input and amplifies the difference. If the feedback voltage is lower than the reference voltage, the pass-transistor gate is pulled low. This increases the PMOS's gate to source voltage and allows more current to pass through the transistor to the output which increases the output voltage. Conversely, if the feedback voltage is higher than the reference voltage, the pass transistor gate is pulled high, decreasing the gate-to-source voltage, thereby allowing less current to pass to the output and causing it to drop.

#### **Internal P-Channel Pass Transistor**

A 0.9  $\Omega$  (typical) P-channel MOSFET is used as the pass transistor for the SiP21106, SiP21107, SiP21108 part series. The MOSFET transistor offers many advantages over the more, formerly, common PNP pass transistor designs, which ultimately result in longer battery lifetime. The main disadvantage of PNP pass transistors is that they require a certain base current to stay on, which significantly increases under heavy load conditions. In addition, during dropout, when the pass transistor saturates, the PNP regulators waste considerable current. In contrast, P-channel MOSFETS require virtually zero-base drive and do not suffer from the stated problems. These savings in base drive current translate to lower quiescent current which is typical around 35  $\mu$ A as shown in the *Typical Characteristics*.

#### Shutdown and Auto-Dischage/No-Discharge

Bringing the EN voltage low will place the part in shutdown mode where the device output enters a high-impedance state and the quiescent current is reduced to below 1  $\mu$ A, reducing the drain on the battery in standby mode and increasing standby time. Connect EN pin to input for normal operation. The output has an internal pull down to discharge the output to ground when the EN pin is low. The internal pull down is a 100  $\Omega$  typical resistor, which can discharge a 1  $\mu$ F in less than 1 ms. Refer to *Typical Operating Waveforms* for turn-off waveforms.

#### **Output Voltage Selection**

The SiP21106 has fixed voltage outputs that are preset to voltages from 1.2 V to 4.6 V (see Ordering Information).

The SiP21108 has a user-adjustable output that can be set through the resistor feedback network consisting of R<sub>1</sub> and R<sub>2</sub>. R<sub>2</sub> range of 100K to 400K is recommended to be consistent with ground current specification. R<sub>1</sub> can then be determined by the following equation:

$$R_1 = R_2 \times \left(\frac{V_{OUT}}{V_{ref}} - 1\right)$$

Where  $V_{ref}$  is typically 1.2005 V. Use 1 % or better resistors for better output voltage accuracy (see Figure 4).

#### Current Limit

The SiP21106, SiP21107, SiP21108 include a current limit block which monitors the current passing through the pass transistor through a current mirror and controls the gate voltage of the MOSFET, limiting the output current to 330 mA (typical). This current limit feature allows for the output to be shorted to ground for an indefinite amount of time without damaging the device.

#### **Thermal-Overload Protection**

The thermal overload protection limits the total power dissipation and protects the device from being damaged. When the junction temperature exceeds  $T_J = 150$  °C, the device turns the P-channel pass transistor off allowing the device to cool down. Once the temperature drops by about 20 °C, the thermal sensor turns the pass transistor on again and resumes normal operation. Consequently, a continuous thermal overload condition will result in a pulsed output. It is generally recommended to not exceed the junction temperature rating of 125 °C for continuous operation.

#### Noise Reduction in SiP21106

For the SiP21106, an external 10 nF bypass capacitor at BP pin is used to create a low pass filter for noise reduction. The startup time is fast, since a power-on circuit pre-charges the bypass capacitor. After the power-up sequence the pre-charge circuit is switched to standby mode in order to save current. It is therefore not recommended to use larger bypass capacitor values than 50 nF. When the circuit is used without a capacitor, stable operation is guaranteed.

Vishay Siliconix

#### POK Status in SiP21107

The POK comparator monitors the output until the supply comes up to specified percentage of V<sub>IN</sub>. This open drain NMOS output requires an external pull-up resistor to either V<sub>OUT</sub> or V<sub>IN</sub>. The internal NMOS can drive up to 0.5 mA loads. POK pin is active high to indicate that output is within percentage tolerance. POK goes low when output is outside of this tolerance as when in dropout, over current and thermal shutdown.

### **APPLICATION INFORMATION**

Input/Output Capacitor Selection and Regulator Stability It is recommended that a low ESR 1 µF capacitor be used on the SiP21106, SiP21107, SiP21108 input. A larger input capacitance with lower ESR would improve noise rejection and line-transient response. A larger input bypass capacitor may be required in applications involving long inductive traces between the source and LDO. The circuit is stable with only a small output capacitor equal to 6 nF/mA (≈ 1 µF at 150 mA) of load. Since the bandwidth of the error amplifier is around 1 MHz - 3 MHz and the dominant pole is at the output node, the capacitor should be capacitive in this range, i.e., for 150 mA load current, an ESR < 0.4  $\Omega$  is necessary. Parasitic inductance of about 10 nH can be tolerated. Applying a larger output capacitor would increase power supply rejection and improve load-transient response. Some ceramic dielectrics such as the Z5U and Y5V exhibit large capacitance and ESR variation over temperature. If such capacitors are used, a 2.2 µF or larger value may be needed to ensure stability over the industrial temperature range. If using higher quality ceramic capacitors, such as those with X7R and Y7R dielectrics, a 1 µF capacitor will be sufficient at all operating temperatures.

#### **Operating Region and Power Dissipation**

An important consideration when designing power supplies is the maximum allowable power dissipation of a part. The maximum power dissipation in any application is dependant on the maximum junction temperature,  $T_{J(max)} = 125$  °C, the ambient temperature,  $T_A$ , and the junction-to-ambient thermal resistance for the package, which is the summation of  $\theta_{J-C}$ , the thermal resistance of the package, and  $\theta_{C-A}$ , the thermal resistance through the PC board and copper traces. Power dissipation may be expressed as:

$$P_{(max)} = \frac{T_{J}(max) - T_{A}}{\theta_{J-C} + \theta_{C-A}}$$

The GND pin of the SiP2110 acts as both the electrical connection to GND as well as a path for channeling away heat. Connect this pin to a GND plane to maximize heat dissipation. Once maximum power dissipation is calculated using the equation above, the maximum allowable output current for any input/output potential can be calculated as

$$I_{OUT(max)} = \frac{P_{(max)}}{V_{IN} - V_{OUT}}$$

#### PCB Layout

The component placement around the LDO should be done carefully to achieve good dynamic line and load response. The input and noise capacitor should be kept close to the LDO. The rise in junction temperature depends on how efficiently the heat is carried away from junction-to-ambient. The junction-to-lead thermal impedance is a characteristic of the package and is fixed. The thermal impedance between lead-to-ambient can be reduced by increasing the copper area on PCB. Increase the input, output and ground trace area to reduce the junction-to-ambient thermal impedance.

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see <a href="http://www.vishay.com/ppg?74442">www.vishay.com/ppg?74442</a>.

**Vishay Siliconix**

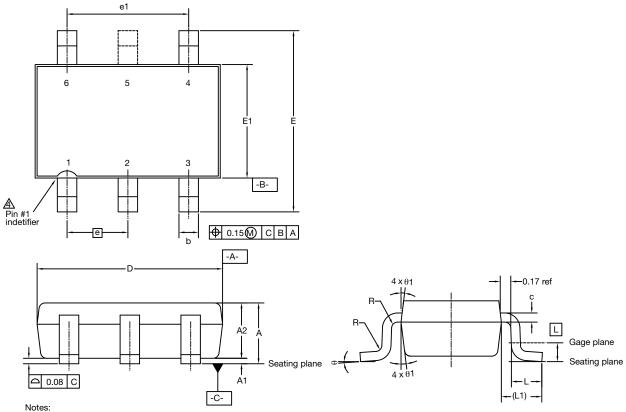

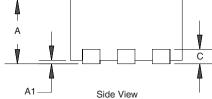

### Thin SOT-23 : 5- and 6-Lead (Power IC only)

1. Use millimeters as the primary measurement.

2. Dimensioning and tolerances conform to ASME Y14.5M. - 1994.

3. This part is fully compliant with JEDEC MO-193.

A Detail of Pin #1 indentifier is optional.

|      |       | MILLIMETERS |      |       | INCHES     |       |  |

|------|-------|-------------|------|-------|------------|-------|--|

| DIM. | MIN.  | NOM.        | MAX. | MIN.  | NOM.       | MAX.  |  |

| А    | 0.91  | 1.00        | 1.10 | 0.036 | 0.039      | 0.043 |  |

| A1   | 0.00  | 0.05        | 0.10 | 0.000 | 0.002      | 0.004 |  |

| A2   | 0.85  | 0.90        | 1.00 | 0.033 | 0.035      | 0.039 |  |

| b    | 0.30  | 0.40        | 0.45 | 0.012 | 0.016      | 0.018 |  |

| С    | 0.10  | 0.15        | 0.20 | 0.004 | 0.006      | 0.008 |  |

| D    | 2.85  | 2.95        | 3.10 | 0.112 | 0.116      | 0.122 |  |

| E    | 2.70  | 2.85        | 2.98 | 0.106 | 0.112      | 0.117 |  |

| E1   | 1.525 | 1.65        | 1.70 | 0.060 | 0.065      | 0.067 |  |

| е    |       | 0.95 BSC    |      |       | 0.0374 BSC |       |  |

| L    | 0.30  | 0.40        | 0.50 | 0.014 | -          | 0.020 |  |

| L1   |       | 0.60 ref.   |      |       | 0.024 BSC  |       |  |

| L2   |       | 0.25 BSC    |      |       | 0.010 BSC  |       |  |

| θ    | 0°    | 4°          | 8°   | 0°    | 4°         | 8°    |  |

| θ1   | 4°    | 10°         | 12°  | 4°    | 10°        | 12°   |  |

Document Number: 72821

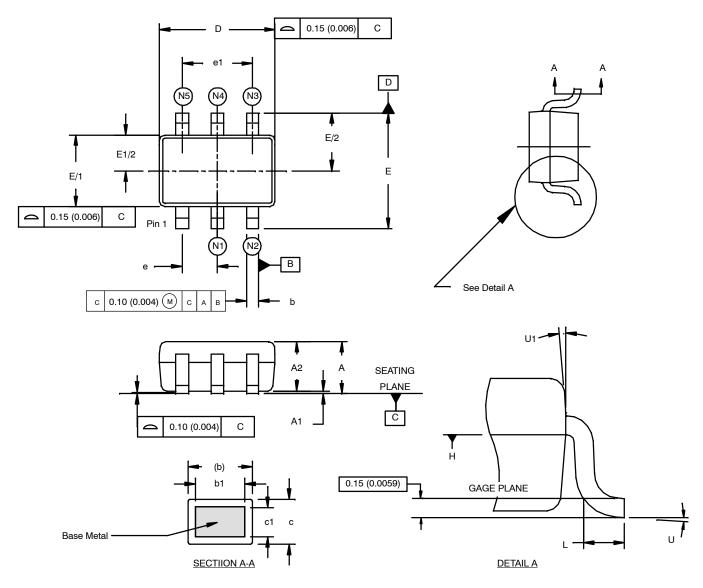

### SC-70: 3/4/5/6-LEADS (PIC ONLY)

| Pin  | LEAD COUNT |   |   |   |  |  |

|------|------------|---|---|---|--|--|

| Code | 3          | 4 | 5 | 6 |  |  |

| N1   | -          | - | 2 | 2 |  |  |

| N2   | 2          | 2 | 3 | 3 |  |  |

| N3   | -          | 3 | 4 | 4 |  |  |

| N4   | 3          | - | - | 5 |  |  |

| N5   | -          | 4 | 5 | 6 |  |  |

#### NOTES:

- 1. Dimensioning and tolerancing per ANSI Y14.5M-1994.

- 2. Controlling dimensions: millimeters converted to inch dimensions are not necessarily exact.

- Dimension "D" does not include mold flash, protrusion or gate burr. Mold flash, protrusion or gate burr shall not exceed 0.15 mm (0.006 inch) per side.

- 4. The package top shall be smaller than the package bottom. Dimension "D" and "E1" are determined at the outer most extremes of the plastic body exclusive of mold flash, tie bar burrs, gate burrs and interlead flash, but including any mismatch between the top and bottom of the plastic body.

|                | Μ    | ILLIMETE |      | INCHES |            |            |  |

|----------------|------|----------|------|--------|------------|------------|--|

| Dim            | Min  | Nom      | Max  | Min    | Nom        | Max        |  |

| Α              | 0.80 | -        | 1.10 | 0.031  | -          | 0.043      |  |

| A1             | 0.00 | -        | 0.10 | 0.000  | -          | 0.004      |  |

| A2             | 0.80 | 0.90     | 1.00 | 0.031  | 0.035      | 0.040      |  |

| b              | 0.15 | -        | 0.30 | 0.006  | -          | 0.012      |  |

| b1             | 0.15 | 0.20     | 0.25 | 0.006  | 0.008      | 0.010      |  |

| С              | 0.08 | -        | 0.25 | 0.003  | -          | 0.010      |  |

| c1             | 0.08 | 0.13     | 0.20 | 0.003  | 0.005      | 0.008      |  |

| D              | 1.90 | 2.10     | 2.15 | 0.074  | 0.082      | 0.084      |  |

| Е              | 2.00 | 2.10     | 2.20 | 0.078  | 0.082      | 0.086      |  |

| E <sub>1</sub> | 1.15 | 1.25     | 1.35 | 0.045  | 0.050      | 0.055      |  |

| е              |      | 0.65 BSC |      |        | 0.0255 BSC |            |  |

| e <sub>1</sub> |      | 1.30 BSC |      |        | 0.0512 BSC |            |  |

| L              | 0.26 | 0.36     | 0.46 | 0.010  | 0.014      | 0.018      |  |

| U              | 0°   | -        | 8°   | 0°     | -          | <b>8</b> ° |  |

| U1             | 4°   |          | 10°  | 4°     |            | 10°        |  |

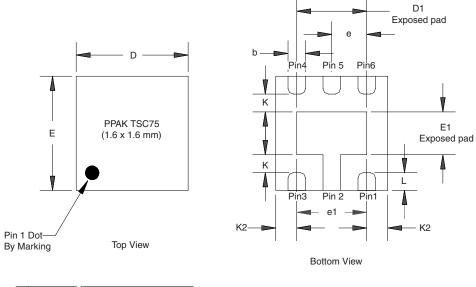

### PowerPAK<sup>®</sup> TSC75-6L (Power IC only)

|                          | MILLIMETERS INCHES                          |          |      |        |           |       |  |  |  |

|--------------------------|---------------------------------------------|----------|------|--------|-----------|-------|--|--|--|

| DIM                      | Min                                         | Nom      | Max  | Min    | Nom       | Max   |  |  |  |

| A                        | 0.50                                        | 0.55     | 0.65 | 0.020  | 0.022     | 0.026 |  |  |  |

| A1                       | 0                                           | -        | 0.05 | 0      | -         | 0.002 |  |  |  |

| b                        | 0.20                                        | 0.25     | 0.30 | 0.008  | 0.010     | 0.012 |  |  |  |

| С                        | 0.10                                        | 0.15     | 0.20 | 0.006  | 0.008     | 0.010 |  |  |  |

| D                        | 1.55                                        | 1.60     | 1.65 | 0.0061 | 0.063     | 0.065 |  |  |  |

| D1                       | 0.95                                        | 1.00     | 1.05 | 0.037  | 0.039     | 0.041 |  |  |  |

| E                        | 1.55                                        | 1.60     | 1.65 | 0.061  | 0.063     | 0.065 |  |  |  |

| E1                       | 0.55                                        | 0.60     | 0.65 | 0.022  | 0.024     | 0.026 |  |  |  |

| е                        |                                             | 0.50 BSC |      |        | 0.020 BSC |       |  |  |  |

| e1                       | 1.00 BSC                                    |          |      |        | 0.039 BSC |       |  |  |  |

| К                        | 0.15                                        | -        | -    | 0.006  | -         | -     |  |  |  |

| K2                       | 0.20                                        | -        | -    | 0.008  |           |       |  |  |  |

| L                        | 0.20                                        | 0.25     | 0.30 | 0.008  | 0.010     | 0.012 |  |  |  |

| ECN: S-6191<br>DWG: 5955 | ECN: S-61919-Rev. A, 02-Oct-06<br>DWG: 5955 |          |      |        |           |       |  |  |  |

Vishay

### Disclaimer

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Hyperlinks included in this datasheet may direct users to third-party websites. These links are provided as a convenience and for informational purposes only. Inclusion of these hyperlinks does not constitute an endorsement or an approval by Vishay of any of the products, services or opinions of the corporation, organization or individual associated with the third-party website. Vishay disclaims any and all liability and bears no responsibility for the accuracy, legality or content of the third-party website or for that of subsequent links.

Vishay products are not designed for use in life-saving or life-sustaining applications or any application in which the failure of the Vishay product could result in personal injury or death unless specifically qualified in writing by Vishay. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

© 2024 VISHAY INTERTECHNOLOGY, INC. ALL RIGHTS RESERVED

Revision: 01-Jul-2024